ZR36015 Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

Список матч

ZR36015 Datasheet PDF : 27 Pages

| |||

PRELIMINARY

ZR36015

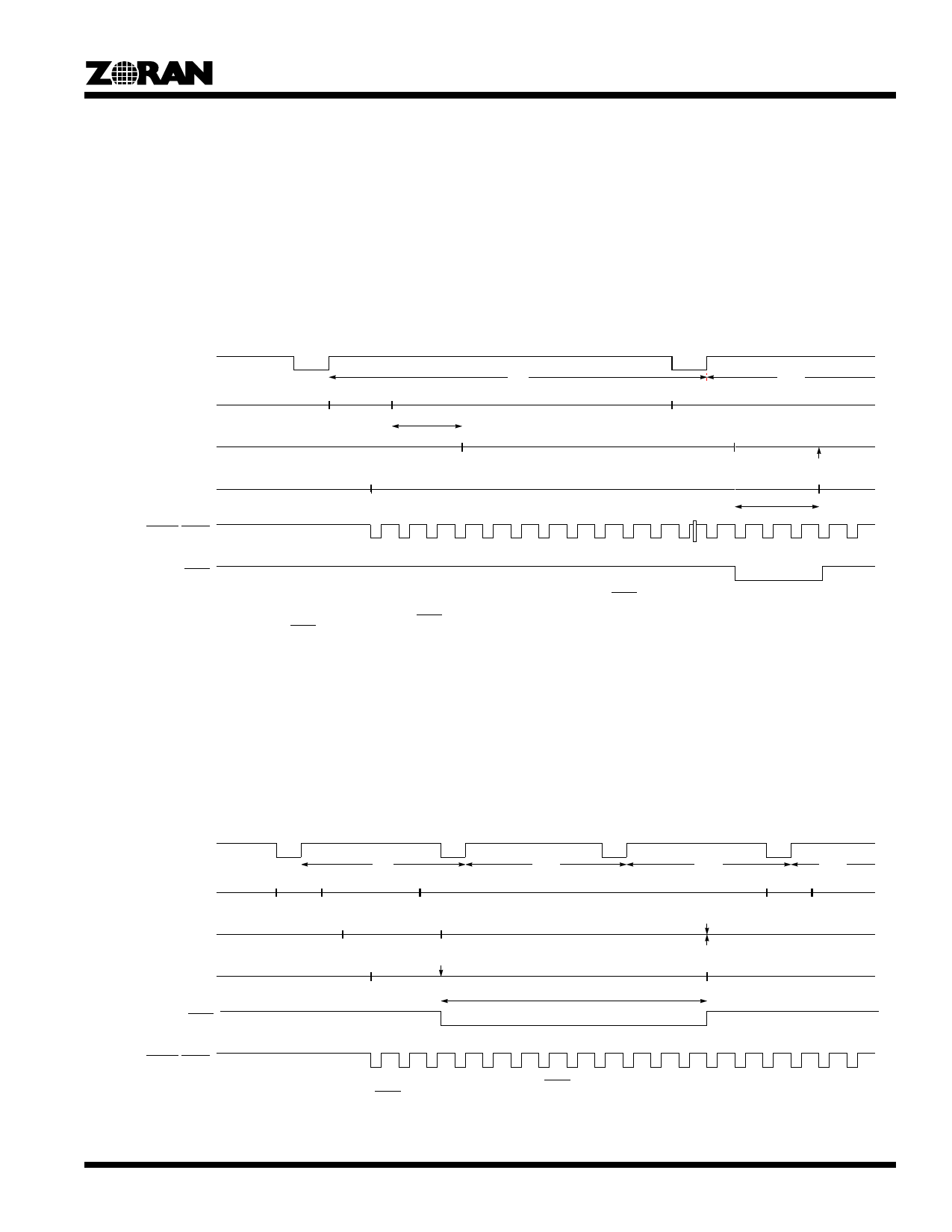

2. DSYNC active indicates that data for Strip Buffer AB (previously loaded) continues to be unloaded to the Coder Bus.

3. The ZR36015 finishes counting HDelay; then data for Strip Buffer A’B’ continues to be loaded from the Pixel bus.

4. The writing of a strip to the A’B’ side of the Strip Buffer is complete. At this time the ZR36015 checks to see if the datat from AB

has been unloaded. In example 3, AB is still in the process of being unloaded, so the CBSY signal is asserted to indicate the the

ZR36015 is not ready to accept more input data from the Pixel side. But before CBSY is asserted, the next HEN signal (for the

first line of the next strip) becomes active.

HEN has become active because the CBSY signal was not asserted in time to stop it. This is due to the HDelay+HWidth values

being the maximum (length of HEN). Also, we’ve assumed that the low period between HENs is minimal.

In example 3, line 8n+1 will be ignored (lost) due to the CBSY signal. The ZR36015 will begin processing the next new input line after

CBSY is de-asserted.

HEN

PXDATA Bus

Write to Strip Buffer

Read From Strip Buffer

DSYNC/ISNYC

NAX

Delay of internal

processing

8n

PAX

PAX

PAX

8n+1

Check if all contents of the coder

side buffer have been read out.

Buffer selection point

Check if all contents of the pixel

side buffer have been entered.

The coder side buffer is

monitored as required

CBSY

1. If PAX + NAX is set to the maximum effective period of HEN as shown above, CBSY may be active on a line following the

8n line (16n line depending on the mode) for the reason of internal delay. In this case, the processing of the line is started

in MD0205, and finished when CBSY is active. In case of the above timing chart, MD0205 ignores the 8n+1 line, waits until

CBSY becomes non-active and resumes processing from the rise of next HEN (8n+2 line).

Figure 14. Example of CBSY Timing - In Encoding (HDelay + HWidth = Width of HEN)

Example #4: Long CBSY, New lines continue to come in

Figure 15 shows an example in enoding mode, where the CBSY signal is active for a long period (this could be the result of the STOP

signal being active for a long period). Also in this example, new lines continue to be input into the ZR36015 (as indicated by the HEN

signal).

In example #4, lines 8n+1 and 8n+2 will be ignored (lost), and processing will continue with line 8n+3.

For system which must not loose lines of data, the new lines of data must be held up and only input after CBSY becomes inactive.

HEN

PXDATA Bus

Write to Strip Buffer

Read From Strip Buffer

CBSY

NAX

8n

PAX

PAX

8n+1

Check if all contents of the coder

side buffer have been read out.

The coder side buffer is monitored as required

8n+2

NAX

8n+3

PAX

Buffer selection point

Check if all contents of the pixel

side buffer have been entered.

DSYNC/ISNYC

1. If the processing at the coder side is substantially delayed and CBSY is outputted for a long period of time as shown above,

all lines which cover CBSY are ignored. Accordingly, in case of the above timing chart, the 8n+1 line and the 8n+2 line are

ignored and the processing is started from the 8n+3 line.

Figure 15. Example of CBSY Timing

13