LH52D1000 Просмотр технического описания (PDF) - Sharp Electronics

Номер в каталоге

Компоненты Описание

Список матч

LH52D1000 Datasheet PDF : 12 Pages

| |||

LH52D1000

CMOS 1M (128K × 8) Static RAM

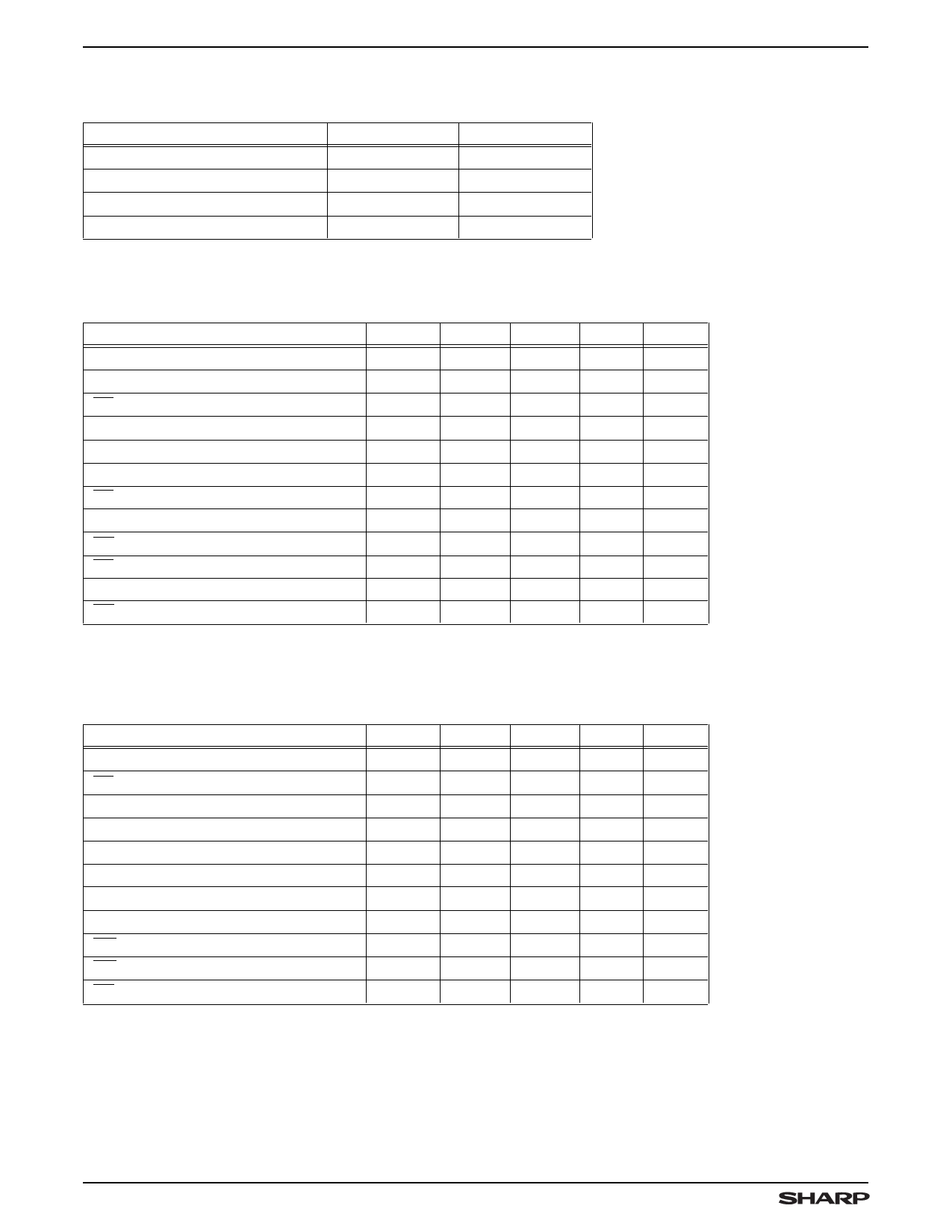

AC ELECTRICAL CHARACTERISTICS

AC Test Conditions

PARAMETER

Input pulse level

Input rise and fall time

Input and output timing Ref. level

Output load

NOTE:

1. Including scope and jig capacitance.

MODE

0.4 V to 2.4 V

5 ns

1.5 V

100 pF + 1TTL

NOTE

1

READ CYCLE (TA = -40°C to +85°C, VCC = 2.7 V to 3.6 V)

PARAMETER

SYMBOL MIN.

MAX.

UNIT NOTE

Read cycle time

tRC

85

ns

Address access time

tAA

85

ns

CE1 access time

tACE1

85

ns

CE2 access time

tACE2

85

ns

Output enable to output valid

tOE

45

ns

Output hold from address change

tOH

10

ns

CE1 Low to output active

tLZ1

5

ns

1

CE2 High to output active

tLZ2

5

ns

1

OE Low to output active

tOLZ

0

ns

1

CE1 High to output in High impedance

tHZ1

0

35

ns

1

CE2 Low to output in High impedance

tHZ2

0

35

ns

1

OE High to output in High impedance

tOHZ

0

35

ns

1

NOTE:

1. Active output to High impedance and High impedance to output active tests specified for a ±200 mV transition

from steady state levels into the test load.

WRITE CYCLE (TA = -40°C to +85°C, VCC = 2.7 V to 3.6 V)

PARAMETER

SYMBOL MIN.

MAX.

UNIT NOTE

Write cycle time

tWC

85

ns

CE1 Low to end of write

tCW1

75

ns

CE2 High to end of write

tCW2

75

ns

Address setup time

tAS

0

ns

Write pulse width

tWP

60

ns

Write recovery time

tWR

0

ns

Input data setup time

tDW

35

ns

Input data hold time

tDH

0

ns

WE High to output active

tOW

0

ns

1

WE Low to output in High impedance

tWZ

0

ns

1

OE High to output in High impedance

tOHZ

0

35

ns

1

NOTE:

1. Active output to High impedance and High impedance to output active tests specified for a ±200 mV transition

from steady state levels into the test load.

4