LH28F320BJE-PTTL90 Просмотр технического описания (PDF) - Sharp Electronics

Номер в каталоге

Компоненты Описание

Список матч

LH28F320BJE-PTTL90 Datasheet PDF : 51 Pages

| |||

SHARP

LHF32JO2

14.12 OTP Program Command

(3TP program is executed by a two-cycle command

Isequence. OTP program command(COH) is written,

1rollowed by a second write cycle that specifies the address

imd data (latched on the rising edge of WE#). The WSM

then takes over, controlling the OTP program and program

\verify algorithms internally. After the OTP program

C:ommand sequence is completed, the device automatically

tutputs status register data when read (see Figure 13). The

; ZPU can detect the completion of the OTP program by

2analyzing the output data of the RY/BY# pin or status

I egister bit SR.7.

\ Nhen OTP program is completed, status register bit SR.4

s hould be checked. If OTP program error is detected, the

Status register should be cleared. The internal WSM verify

Conly detects errors for “1”s that do not successfully

Fbrogram to “0”s. The CUI remains in read status register

nnode until it receives other commands.

Fleliable OTP program can be executed only when

\ I,,=2.7V-3.6V and VCCw=VCCWHln. In the absence of

tlhis voltage, memory contents are protected against OTP

programs. If OTP program is attempted whik

Vccw5Vt--,,.

status register bits SR.3 and SR.4 is se

to “1”. If OTP write is attempted when the OTP Lock-bi

is set, SR.l and SR.4 is set to “1”.

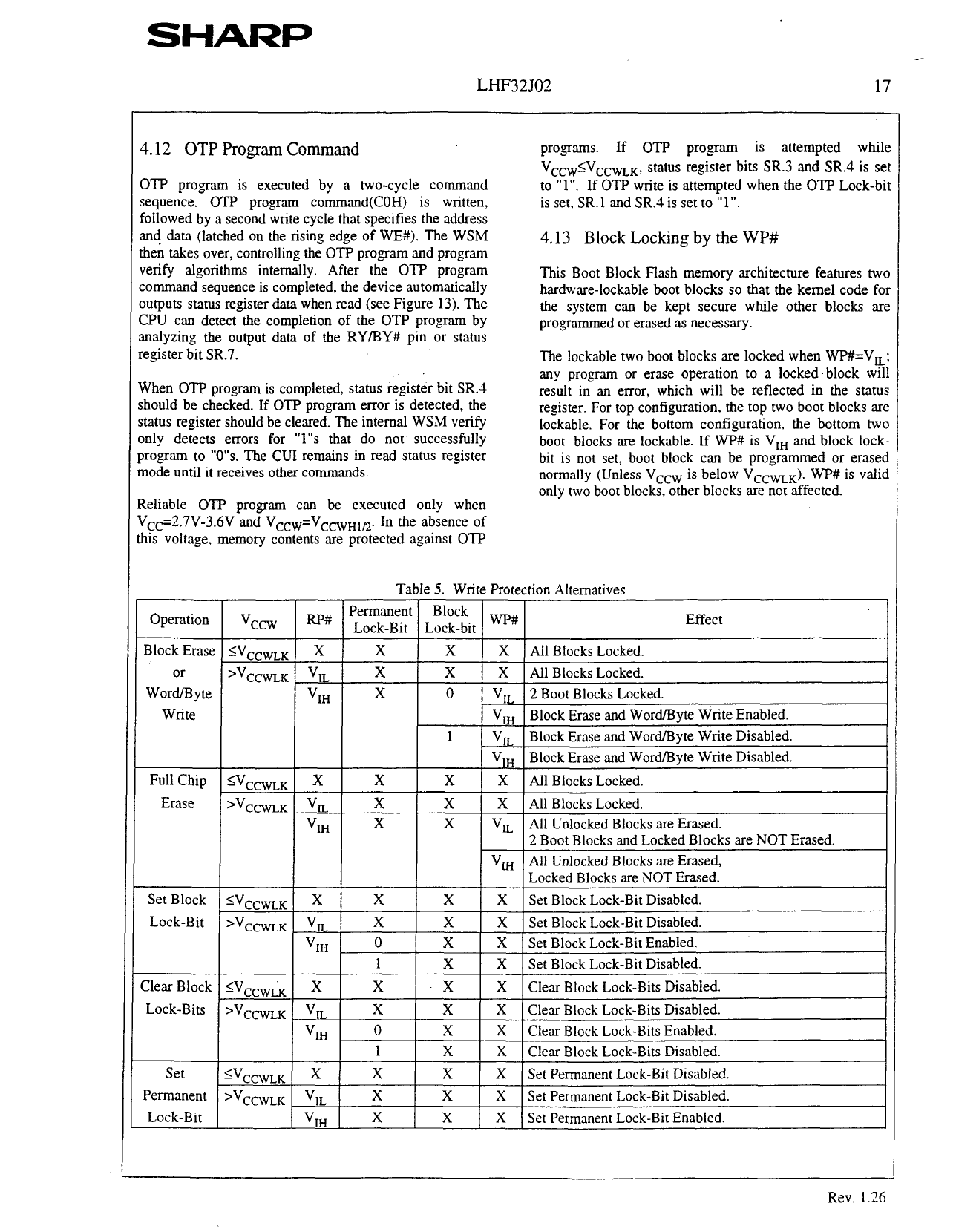

4.13 Block Locking by the WP#

This Boot Block Flash memory architecture features twc

hardware-lockable boot blocks so that the kernel code foi

the system can be kept secure while other blocks arc

programmed or erased as necessary.

The lockable two boot blocks are locked when WP#=V,,

any program or erase operation to a locked ‘block will

result in an error, which will be reflected in the status

register. For top configuration, the top two boot blocks are

lockable. For the bottom configuration, the bottom twc

boot blocks are lockable. If WP# is V, and block lock.

bit is not set, boot block can be programmed or erased

normally (Unless V,, is below VCCwtK). WP# is valid

only two boot blocks, other blocks are not affected.

Table 5. Write Protection Alternatives

Rev. 1.26