CDB42406 Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CDB42406 Datasheet PDF : 32 Pages

| |||

CDB42406

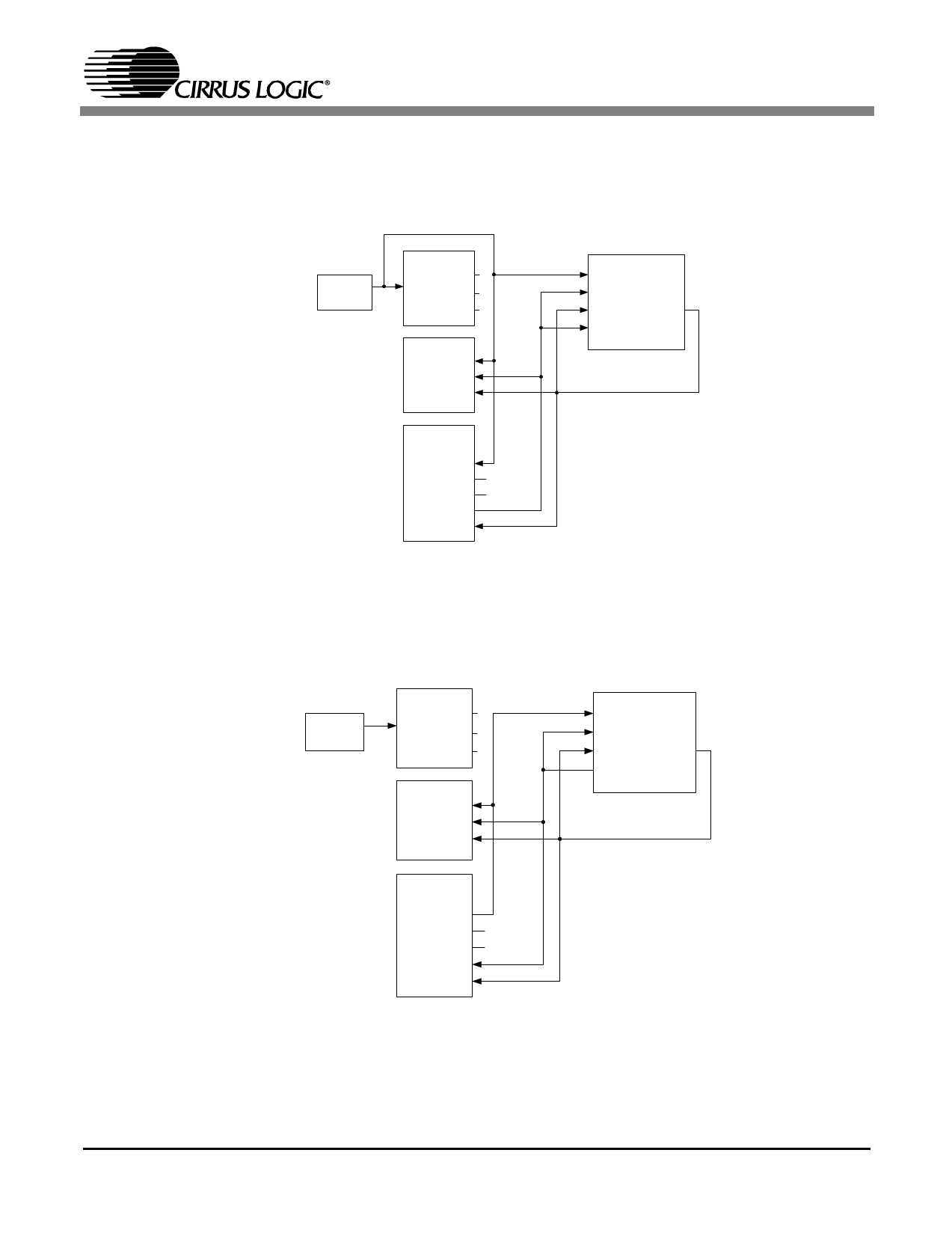

1.7.2b Setup 4

Using the on-board crystal oscillator, AUDIO MCLK, a DSP connected to DSP I/O HDR

masters the subclocks for the ADC/DAC. For implementation of this setup option, set DIP

switch S4 (SW[3:0]) to ‘0100’b.

AUDIO

MCLK

CS8416

RMC K

OMCK

OLRCK/

OSCLK

SDOUT

CS8406

OMCK

ILR CK/

IS CLK

S DIN

CS42406

MCLK

DAC_LRCK/

DAC_SC LK

DAC_SD IN x

A DC_LRCK/

A DC_SCLK

ADC_SDOUT

DSP I/O

HDR

DS P_M CLK

DSP_DA C_LR CK/

DSP_DAC _S CLK

DSP _S DINx

DSP_A DC_LR CK/

DSP_ADC _S CLK

D SP_SDOUT

Figure 5. Digital Loopback - Setup 4

1.7.2c Setup 5

Using the master clock from an external DSP connected to the DSP I/O HDR,

DSP_MCLK, the CS42406 ADC masters the subclocks and data for the DAC. For imple-

mentation of this setup option, set DIP switch S4 (SW[3:0]) to ‘0101’b.

AUDIO

MCLK

CS8416

RM CK

OMCK

OL RC K /

OSCLK

S DO U T

CS8406

OM CK

IL RC K /

IS C LK

SD IN

CS42406

M C LK

DAC_LRCK/

DAC_SCLK

D A C _S D INx

ADC_L RCK/

AD C _S C LK

A D C_ S DO U T

DSP I/O

HDR

DSP_ MCLK

DSP_ DAC_L RCK/

DSP_ DAC_SCLK

D S P _S D IN x

DSP_ ADC_L RCK/

DSP_ ADC_SCLK

D S P _S DO U T

Figure 6. Digital Loopback - Setup 5

9