CDB42406 Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CDB42406 Datasheet PDF : 32 Pages

| |||

CDB42406

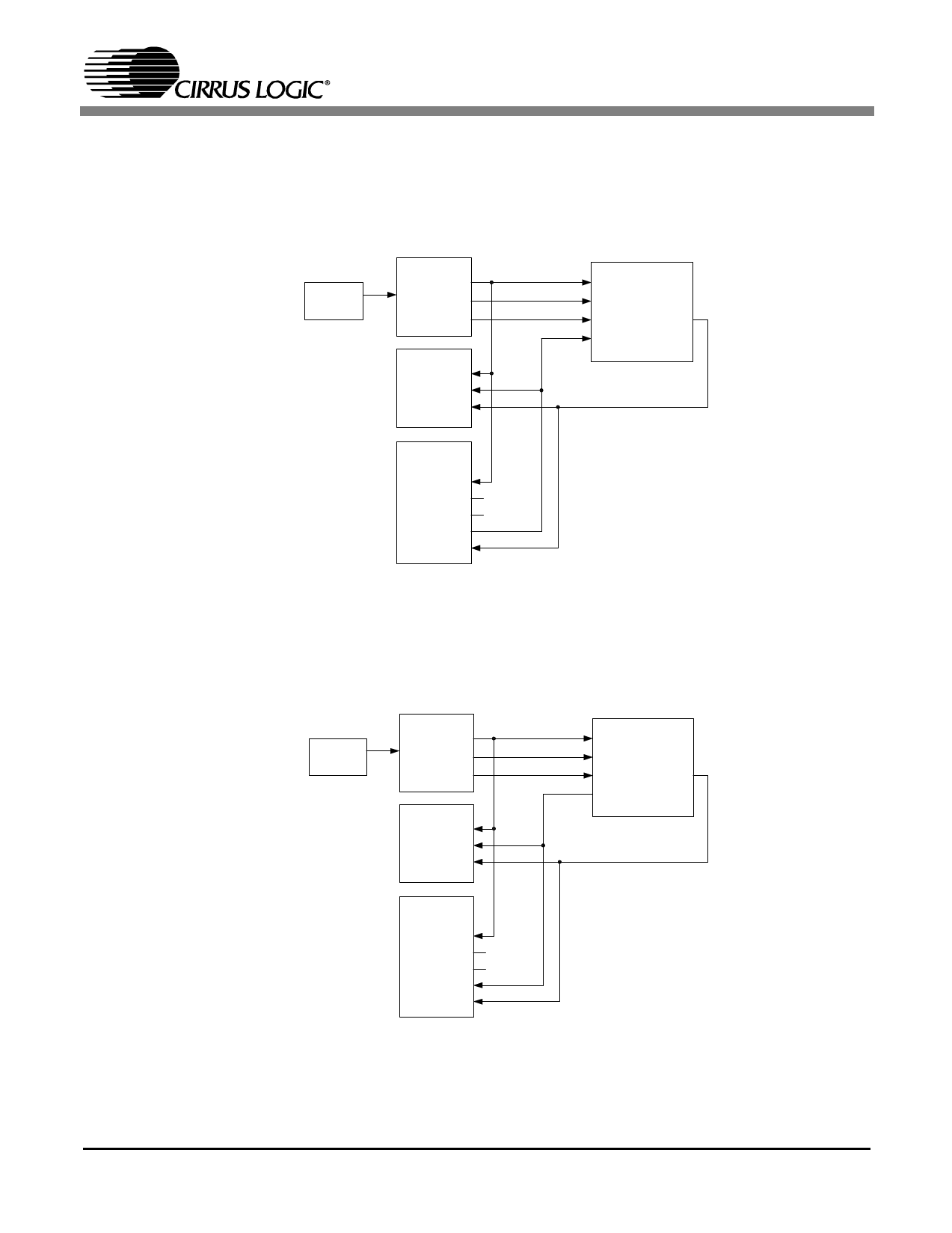

1.7.1b Setup 1

Using the recovered clock from the S/PDIF input data stream, the CS8416 masters MCLK,

subclocks and data for the DAC. A DSP connected to the DSP I/O HDR masters the sub-

clocks for the ADC and CS8406. For implementation of this setup option, set DIP switch

S4 (SW[3:0]) to ‘0001’b.

A U D IO

MCLK

CS8416

RMCK

OMCK

OL RC K /

O SCLK

SDOUT

CS8406

OM CK

IL RC K /

IS C LK

SD IN

CS42406

MCLK

DA C _LR C K/

DA C _S CL K

DA C _S DI Nx

A DC _L RC K /

A DC _S C LK

A D C_ S DO UT

DSP I/O

HDR

DSP_MCLK

DSP_DAC_L RCK/

DS P _D A C_S C LK

DS P _S D IN x

DS P _A DC _L RC K /

DS P _A D C_S C LK

DS P _S D OU T

Figure 2. S/PDIF IN/OUT - Setup 1

1.7.1c Setup 2

Using the recovered clock from the S/PDIF input data stream, the CS8416 masters MCLK,

subclocks and data for the DAC. The ADC masters its own subclocks. For implementation

of this setup option, set DIP switch S4 (SW[3:0]) to ‘0010’b.

AUDIO

MCLK

CS8416

RM C K

OMCK

O LRC K /

O SCLK

SDOUT

CS8406

OMCK

I LRC K/

I SC LK

SD IN

CS42406

MCLK

DA C _LR CK /

DA C _S CLK

DA C _S DIN x

A DC _LR C K/

A DC _S CL K

A DC _S DO UT

DSP I/O

HDR

DS P _M C LK

DSP_ DAC_ LRCK/

DSP_ DAC_ SCLK

D S P_S D INx

DSP_ ADC_ LRCK/

DSP_ ADC_ SCLK

D SP _S D OU T

Figure 3. S/PDIF IN/OUT - Setup 2

7