BS616UV2019(2004) Просмотр технического описания (PDF) - Brilliance Semiconductor

Номер в каталоге

Компоненты Описание

Список матч

BS616UV2019 Datasheet PDF : 9 Pages

| |||

BSI

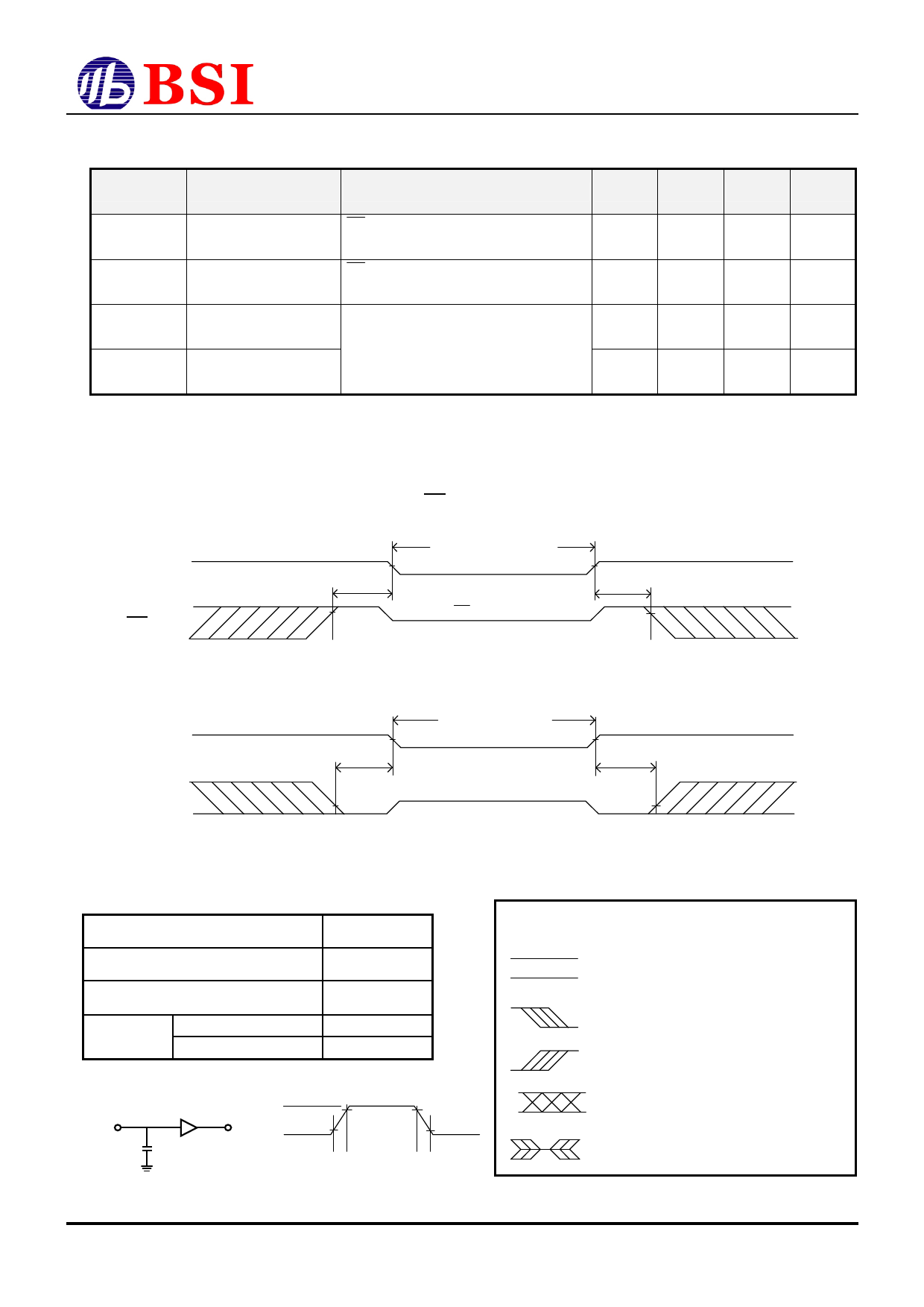

LOW VCC DATA RETENTION WAVEFORM ( CE Controlled )

Vcc

CE

Vcc

t CDR

VIH

Data Retention Mode

VDR ≥ 1.0V

CE ≥ Vcc - 0.2V

BS616UV2019

Vcc

tR

VIH

AC TEST CONDITIONS

(Test Load and Input/Output Reference)

Input Pulse Levels

Vcc / 0V

Input Rise and Fall Times

1V/ns

Input and Output

Timing Reference Level

Output Load

0.5Vcc

CL = 100pF+1TTL

CL = 30pF+1TTL

KEY TO SWITCHING WAVEFORMS

WAVEFORM

INPUTS

MUST BE

STEADY

MAY CHANGE

FROM H TO L

MAY CHANGE

FROM L TO H

,

DON T CARE:

ANY CHANGE

PERMITTED

DOES NOT

APPLY

OUTPUTS

MUST BE

STEADY

WILL BE

CHANGE

FROM H TO L

WILL BE

CHANGE

FROM L TO H

CHANGE :

STATE

UNKNOWN

CENTER

LINE IS HIGH

IMPEDANCE

”OFF ”STATE

AC ELECTRICAL CHARACTERISTICS ( TA = -40 to + 85oC )

READ CYCLE ( 48B BGA ignore CE2 condition)

JEDEC

PARAMETER

NAME

t

AVAX

t

AVQV

t

ELQV

t

BA

t

GLQV

t

E1LQX

t

BE

t

GLQX

t

EHQZ

t

BDO

t

GHQZ

t

AXOX

PARAMETER

NAME

t

RC

t

AA

t

ACS1 , 2

t (1)

BA

t

OE

t

CLZ

t

BE

t

OLZ

t

CHZ

t

BDO

t

OHZ

t

OH

DESCRIPTION

Read Cycle Time

Address Access Time

Chip Select Access Time

Data Byte Control Access Time

Output Enable to Output Valid

Chip Select to Output Low Z

Data Byte Control to Output Low Z

Output Enable to Output in Low Z

Chip Deselect to Output in High Z

Data Byte Control to Output High Z

Output Disable to Output in High Z

Data Hold from Address Change

CYCLE TIME : 100ns

(Vcc = 1.9~3.6V)

MIN. TYP. MAX.

100 --

--

--

-- 100

(CE,CE2) --

-- 100

(LB,UB) --

-- 50

--

-- 50

(CE,CE2) 15 --

--

(LB,UB) 15 --

--

15 --

--

(CE,CE2) --

--

40

(LB,UB) --

--

40

--

--

35

15 --

--

CYCLE TIME : 85ns

(Vcc = 1.9~3.6V)

MIN. TYP. MAX.

85 --

--

--

-- 85

--

-- 85

--

-- 40

--

-- 40

15 --

--

15 --

--

15 --

--

--

--

35

--

--

35

--

--

30

15 --

--

UNIT

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

NOTE :

1. tBA is 50ns/40ns (@speed=100ns/85ns) with address toggle. ; tBA is 100ns/85ns (@speed=100ns/85ns) without address toggle.

R0201-BS616UV2019

4

Revision 1.1

Jan. 2004