V320USC-75LPREVB1 Просмотр технического описания (PDF) - QuickLogic Corporation

Номер в каталоге

Компоненты Описание

Список матч

V320USC-75LPREVB1

V320USC-75LPREVB1 Datasheet PDF : 18 Pages

| |||

V320USC Universal System Controller Rev. G

Timing Parameters

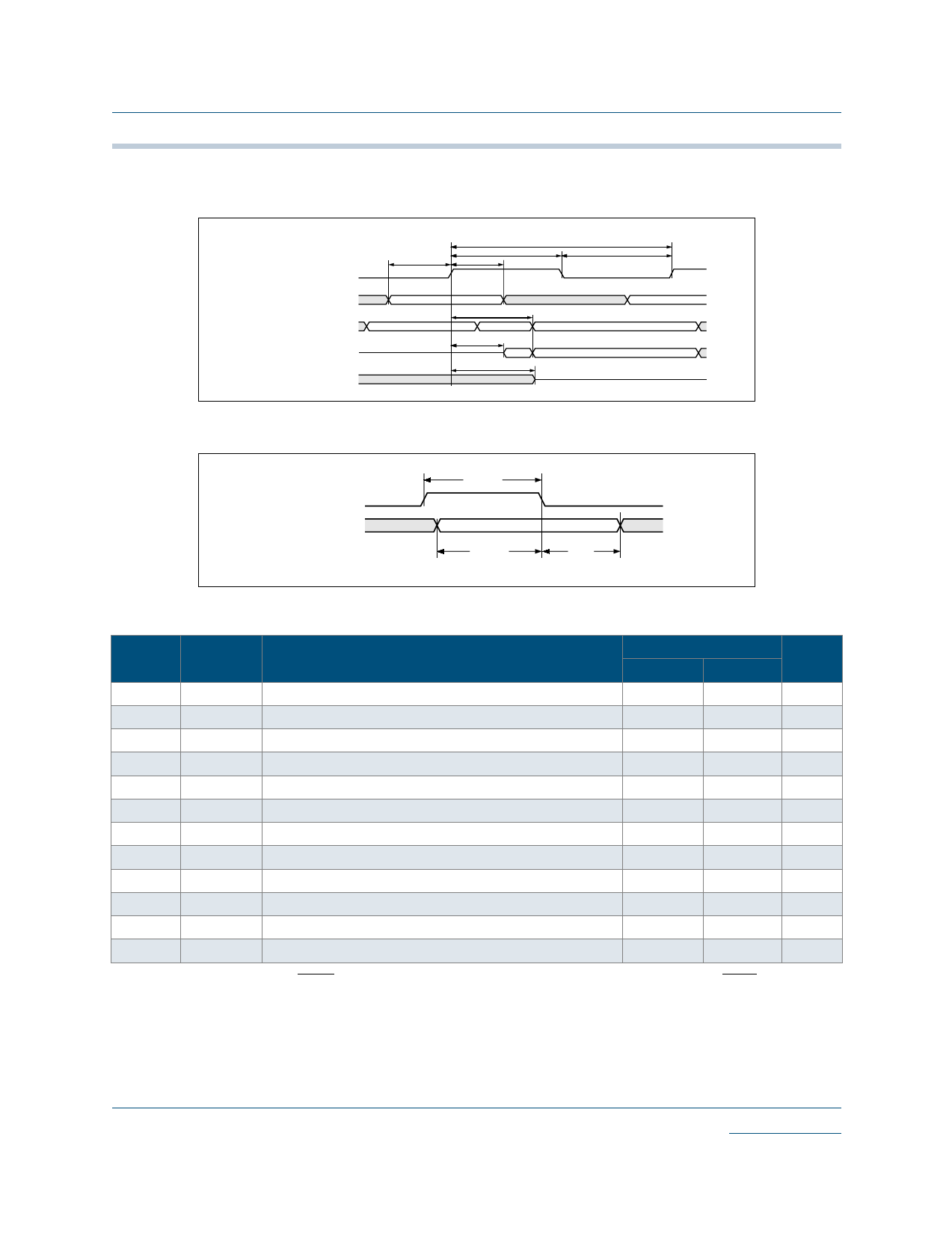

Figure 1: Clock and Synchronous Signals

LOCAL CLOCK

INPUT SETUP/HOLD

OUTPUT VALID

OUTPUT DRIVE

OUTPUT FLOAT

TSU

TC

TCH

TH

VALID

TCOV

;;;;;;;;;;;

Tcz;o;;;;;;;;;;

;;;;;;

TCOZ ;;;;;;

TCL

VALID

VALID

Figure 2: ALE Timing

ALE

MAD

TALE

ADDRESS

TASU

TAH

:

Table 18: Local Bus/M-Bus Timing Parameters for Vcc =3.3 Volts +/- 5%

Number Symbol

Description

1

TC

LCLK period

2

TCH

LCLK high time

3

TCL

LCLK low time

4

TSU

Synchronous input setup

4a

TSU

Synchronous input setup for non-pipelined signalsa

5

TH

Synchronous input hold

6

TCOV LCLK to output valid delay

7

TCZO LCLK to output driving delay

8

TCOZ LCLK to high impedance delay

9

TALE

ALE pulse width

10

TASU

Address to ALE setup time

11

TAH

Address hold time from ALE

75 MHz

Min.

Max.

13.33

4.5

4.5

2.5

9

1.5

9

9

12

TCH-1

TCH

TCL-4

TCH+2

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

a. Non-pipelined signals include MRDY when the SYNC_RDY bit in the LB_BUS_CFG register is ‘0’, and BGNT when the

BREQ_SYNC register is ‘1’.

© 2005 QuickLogic Corporation

www.quicklogic.com

•

•••

••

9