RV5C386A-E2 Просмотр технического описания (PDF) - RICOH Co.,Ltd.

Номер в каталоге

Компоненты Описание

Список матч

RV5C386A-E2 Datasheet PDF : 42 Pages

| |||

RV5C386A

PRELIMINARY

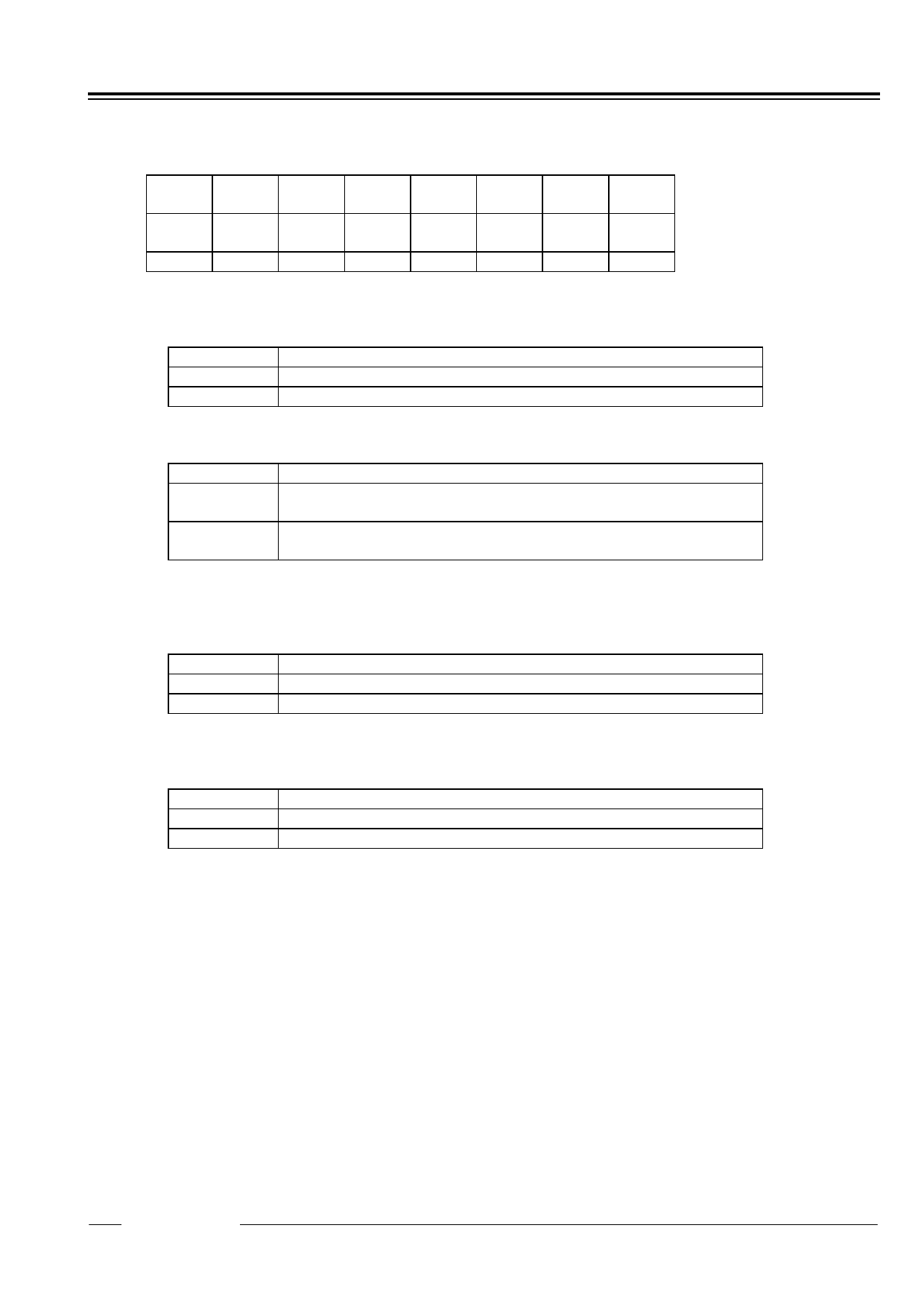

13.2.2. Control Register 2 (Address Fh)

D7

D6

D5

D4

D3

D2

D1

D0

VDSL VDET SCRA- XSTP SCRA- CTFG WAFG DAFG (For Writing)

TCH1

TCH2

VDSL VDET SCRA- XSTP SCRA- CTFG WAFG DAFG (For Reading)

TCH1

TCH2

0

0

0

1

0

0

0

0

Default Settings *)

*) Default settings: Default value means read / written values when the XSTP bit is reset due to power-on from

0 volts or supply voltage drop.

(1) VDSL

Supply Voltage Monitoring Threshold Selection Bit

VDSL

Description

0

Selecting the supply voltage monitoring threshold setting of 2.1v.

1

Selecting the supply voltage monitoring threshold setting of 1.6v.

The VDSL bit is intended to select the supply voltage monitoring threshold settings.

(Default)

(2) VDET

Supply Voltage Monitoring Result Indication Bit

VDET

Description

0

Indicating supply voltage above the supply voltage monitoring

(Default)

threshold settings.

1

Indicating supply voltage below the supply voltage monitoring

threshold settings.

Once the VDET bit is set to 1, the supply voltage monitoring circuit will be disabled while the VDET bit will hold the

setting of 1. The VDET bit accepts only the writing of 0, which restarts the supply voltage monitoring circuit.

Conversely, setting the VDET bit to 1 causes no event.

(3) SCRATCH1 Scratch Bit 1

SCRATCH1

Description

0

(Default)

1

The SCRATCH1 bit is intended for scratching and accepts the reading and writing of 0 and 1. The SCRATCH1

bit will be set to 0 when the XSTP bit is set to 1 in the Control Register 2.

(4) XSTP

Oscillation Halt Sensing Bit

XSTP

Description

0

Sensing a normal condition of oscillation

1

Sensing a halt of oscillation

The XSTP bit is for sensing a halt in the oscillation of the crystal oscillator.

(Default)

* The XSTP bit will be set to 1 once a halt in the oscillation of the crystal oscillator is caused by such events as

power-on from 0 volts and a drop in supply voltage. The XSTP bit will hold the setting of 1 even after the

restart of oscillation. As such, the XSTP bit can be applied to judge the validity of clock and calendar data

after power-on or a drop in supply voltage.

* When the XSTP bit is set to 1, all bits will be reset to 0 in the Oscillation Adjustment Register, Control Register

1, and Control Register 2, stopping the output from /INTRA and /INTRB pins and starting the output of

32.768-kHz clock pulses from the 32KOUT pin.

* The XSTP bit accepts only the writing of 0, which restarts the oscillation halt sensing circuit. Conversely,

setting the XSTP bit to 1 causes no event.

* It is recommendable to frequently check the XSTP bit for setting errors or data garbles, which may seriously

affect the operation of the RV5C386A.

12345

- 12 -