ADM4850 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

Список матч

ADM4850 Datasheet PDF : 16 Pages

| |||

ADM4850/ADM4851/ADM4852/ADM4853/ADM4854/ADM4855/ADM4856/ADM4857

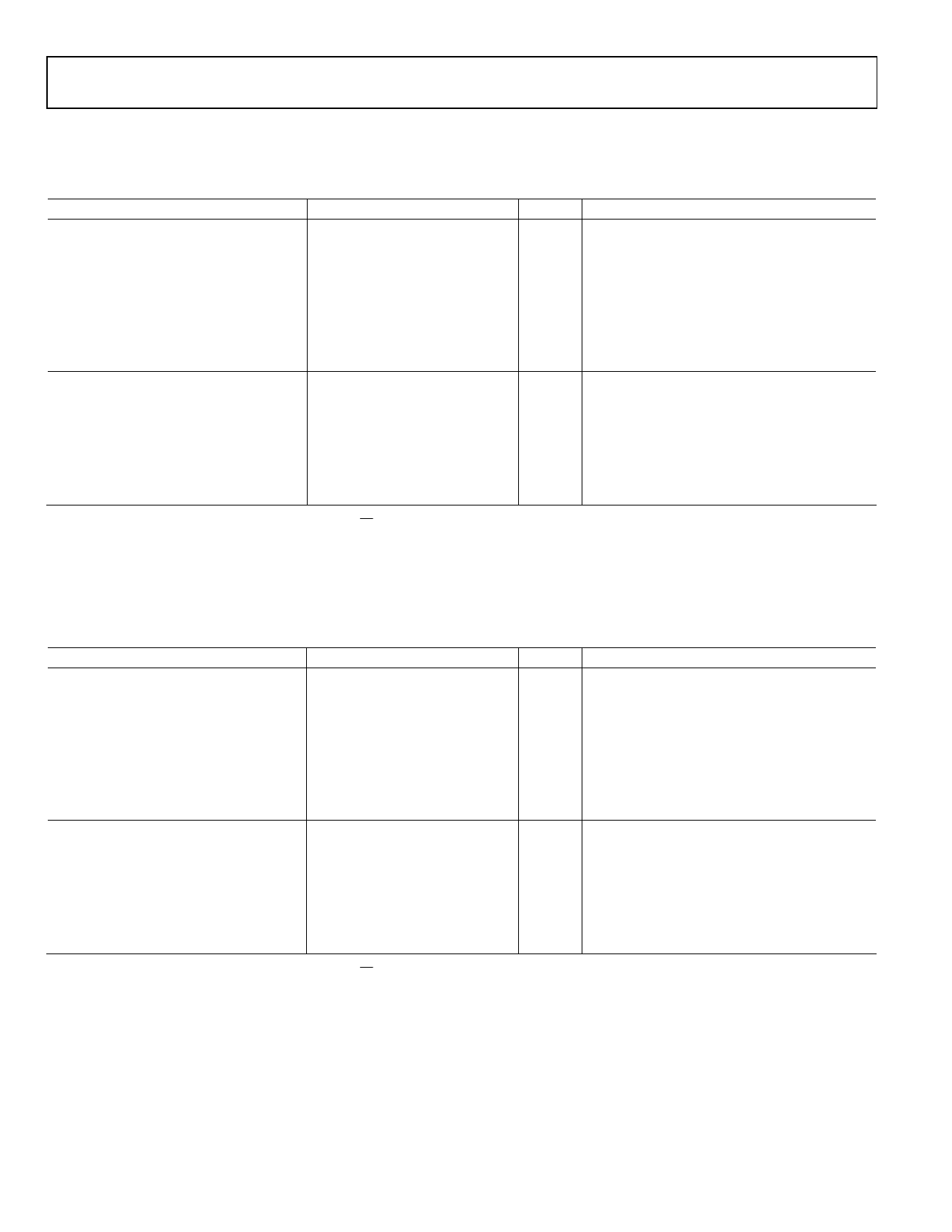

ADM4850/ADM4854 TIMING SPECIFICATIONS

VCC = 5 V ± 5%, TA = TMIN to TMAX, unless otherwise noted.

Table 3.

Parameter

DRIVER

Maximum Data Rate

Propagation Delay, tPLH, tPHL

Skew, tSKEW

Rise/Fall Times, tR, tF

Enable Time, tZH

Disable Time, tZL

Enable Time from Shutdown

RECEIVER

Propagation Delay, tPLH, tPHL

Differential Skew, tSKEW

Enable Time

Disable Time

Enable Time from Shutdown

Time to Shutdown

Min

Typ

Max

Unit

Test Conditions/Comments

115

kbps

600

2500

ns

RLDIFF = 54 Ω, CL1 = CL2 = 100 pF, see Figure 20

70

ns

RLDIFF = 54 Ω, CL1 = CL2 = 100 pF, see Figure 20

600

2400

ns

RLDIFF = 54 Ω, CL1 = CL2 = 100 pF, see Figure 20

2000

ns

RL = 500 Ω, CL = 100 pF, see Figure 21, ADM4850

2000

ns

RL = 500 Ω, CL = 15 pF, see Figure 21, ADM4850

4000

ns

RL = 500 Ω, CL = 100 pF, see Figure 21, ADM4850

400

1000

ns

CL = 15 pF, see Figure 22

255

ns

CL = 15 pF, see Figure 22

5

50

ns

RL = 1 kΩ, CL = 15 pF, see Figure 23, ADM4850

20

50

ns

RL = 1 kΩ, CL = 15 pF, see Figure 23, ADM4850

4000

ns

RL = 1 kΩ, CL = 15 pF, see Figure 23, ADM4850

50

330

3000

ns

ADM48501

1 The half-duplex device is put into shutdown mode by driving RE high and DE low. If these inputs are in this state for less than 50 ns, the device is guaranteed not to

enter shutdown mode. If the enable inputs are in this state for at least 3000 ns, the device is guaranteed to enter shutdown mode.

ADM4851/ADM4855 TIMING SPECIFICATIONS

VCC = 5 V ± 5%, TA = TMIN to TMAX, unless otherwise noted.

Table 4.

Parameter

DRIVER

Maximum Data Rate

Propagation Delay, tPLH, tPHL

Skew, tSKEW

Rise/Fall Times, tR, tF

Enable Time, tZH

Disable Time, tZL

Enable Time from Shutdown

RECEIVER

Propagation Delay, tPLH, tPHL

Differential Skew, tSKEW

Enable Time

Disable Time

Enable Time from Shutdown

Time to Shutdown

Min

Typ

Max

Unit

Test Conditions/Comments

500

kbps

250

600

ns

RLDIFF = 54 Ω, CL1 = CL2 = 100 pF, see Figure 20

40

ns

RLDIFF = 54 Ω, CL1 = CL2 = 100 pF, see Figure 20

200

600

ns

RLDIFF = 54 Ω, CL1 = CL2 = 100 pF, see Figure 20

1000

ns

RL = 500 Ω, CL = 100 pF, see Figure 21, ADM4851

1000

ns

RL = 500 Ω, CL = 15 pF, see Figure 21, ADM4851

4000

ns

RL = 500 Ω, CL = 100 pF, see Figure 21, ADM4851

400

1000

ns

CL = 15 pF, see Figure 22

250

ns

CL = 15 pF, see Figure 22

5

50

ns

RL = 1 kΩ, CL = 15 pF, see Figure 23, ADM4851

20

50

ns

RL = 1 kΩ, CL = 15 pF, see Figure 23, ADM4851

4000

ns

RL = 1 kΩ, CL = 15 pF, see Figure 23, ADM4851

50

330

3000

ns

ADM48511

1 The half-duplex device is put into shutdown mode by driving RE high and DE low. If these inputs are in this state for less than 50 ns, the device is guaranteed not to

enter shutdown mode. If the enable inputs are in this state for at least 3000 ns, the device is guaranteed to enter shutdown mode.

Rev. D | Page 4 of 16