VT82C586B Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

Список матч

VT82C586B Datasheet PDF : 69 Pages

| |||

9,$7HFKQRORJLHV,QF

VT82C586B

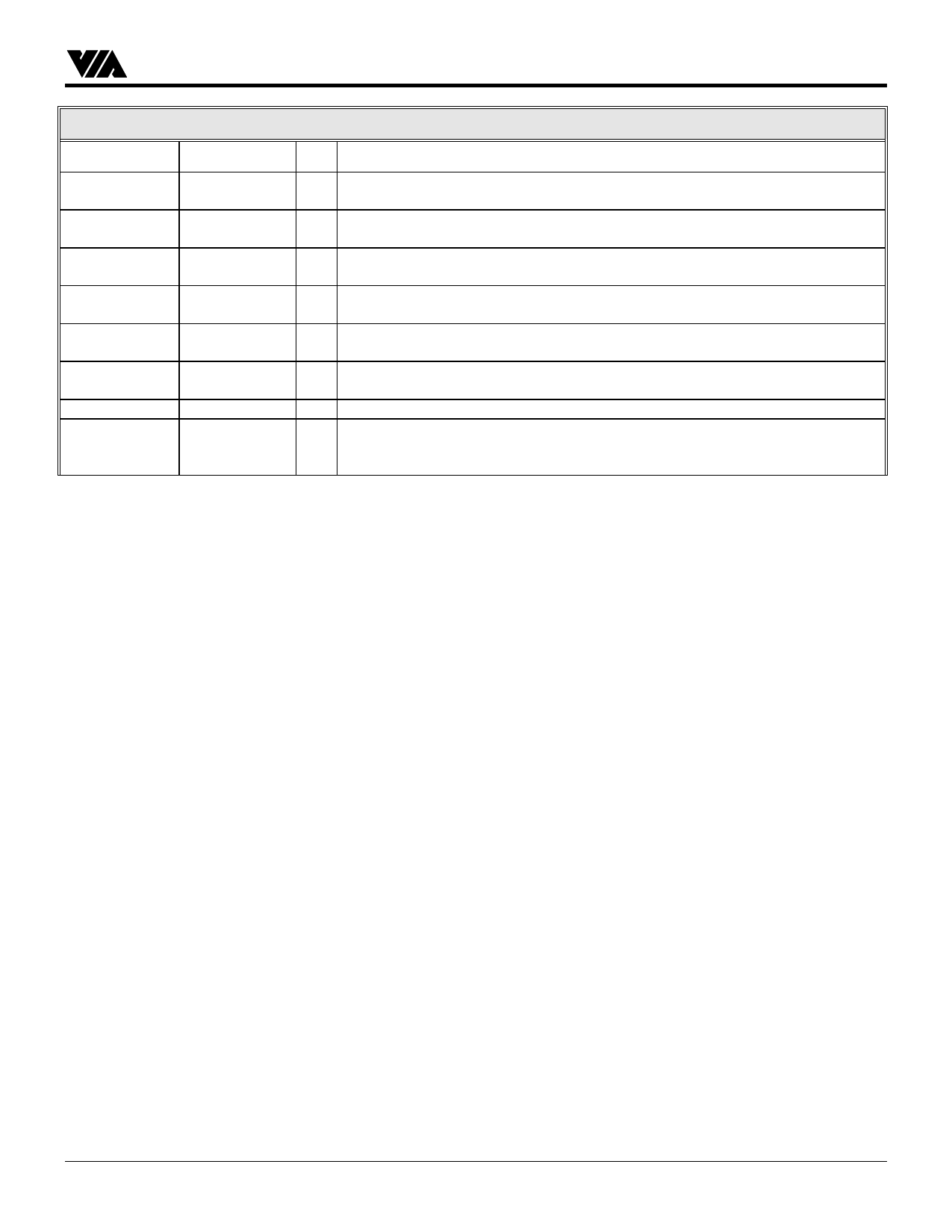

Signal Name

REFRESH#

AEN

IRQ15, 14, 11-

9, 7-3

DRQ7-5, 3-0

DACK7:5, 3-0#

TC

MASTER#

SPKR /

Power-up Strap

Pin No.

29

15

128-129, 127-

126, 61, 71-75

132, 130, 57,

30, 7, 16, 59

133, 131, 58,

31, 33, 18, 60

32

(see below)

134

ISA Bus Control (continued)

I/O Signal Description

B Refresh. As an output REFRESH# indicates when a refresh cycle is in progress. As

an input REFRESH# is driven by 16-bit ISA Bus masters to indicate refresh cycle.

O Address Enable. AEN is asserted during DMA cycles to prevent I/O slaves from

misinterpreting DMA cycles as valid I/O cycles.

I Interrupt Request. The IRQ signals provide both system board components and

ISA Bus I/O devices with a mechanism for asynchronously interrupting the CPU.

I DMA Request. The DRQ lines are used to request DMA services from the

VT82C586B’s DMA controller.

O Acknowledge. The DACK# output lines indicate a request for DMA service has

been granted.

O Terminal Count. The VT82C586B asserts TC to DMA slaves as a terminal count

indicator.

I ISA Master Request. (see below pin 137)

B Multifunction Pin

Normal Operation: Speaker Drive. The SPKR signal is the output of counter 2.

Power-up Strapping: 0/1 = Fixed/flexible IDE I/O base

Revision 1.0 May 13, 1997

-8-

Pinouts