VT82C586B Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

Список матч

VT82C586B Datasheet PDF : 69 Pages

| |||

9,$7HFKQRORJLHV,QF

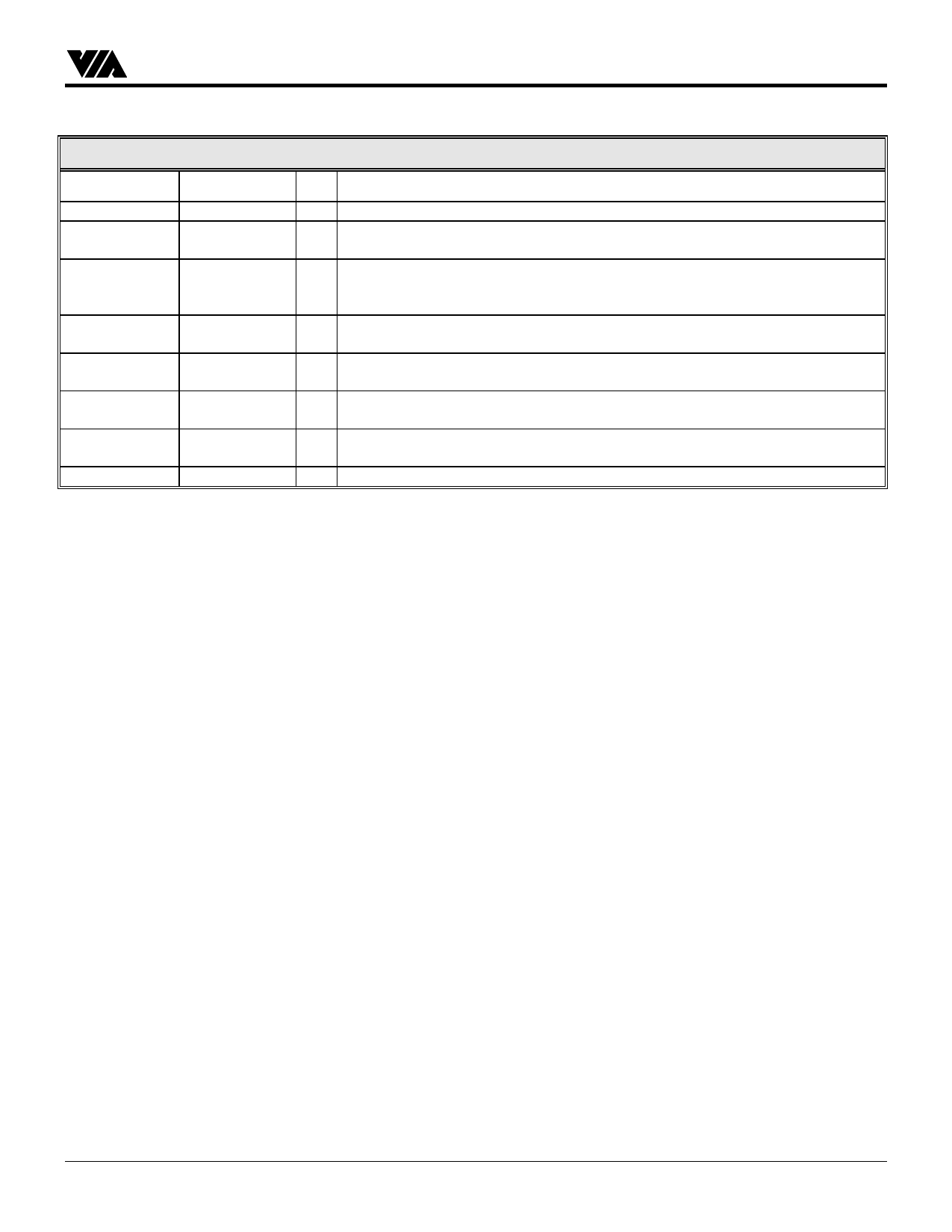

VT82C586B

Signal Name

CPURST

INTR

NMI

INIT

STPCLK#

SMI#

FERR#

IGNNE#

Pin No.

142

145

146

143

148

149

141

139

Table 1. Pin Descriptions

CPU Interface

I/O Signal Description

O CPU Reset. The VT82C586B asserts CPURST to reset the CPU during power-up.

O CPU Interrupt. INTR is driven by the VT82C586B to signal the CPU that an

interrupt request is pending and needs service.

O Non-Maskable Interrupt. NMI is used to force a non-maskable interrupt to the

CPU. The VT82C586B generates an NMI when either SERR# or IOCHK# is

asserted.

O Initialization. The VT82C586B asserts INIT if it detects a shut-down special cycle

on the PCI bus or if a soft reset is initiated by the register

O Stop Clock. STPCLK# is asserted by the VT82C586B to the CPU in response to

different Power-Management events.

O System Management Interrupt. SMI# is asserted by the VT82C586B to the CPU

in response to different Power-Management events.

O Numerical Coprocessor Error. This signal is tied to the coprocessor error signal on

the CPU.

O Ignore Numeric Error. This pin is connected to the “ignore error” pin on the CPU.

Revision 1.0 May 13, 1997

-5-

Pinouts