PHB101NQ04T Просмотр технического описания (PDF) - NXP Semiconductors.

Номер в каталоге

Компоненты Описание

Список матч

PHB101NQ04T Datasheet PDF : 12 Pages

| |||

NXP Semiconductors

PHB101NQ04T

N-channel TrenchMOS standard level FET

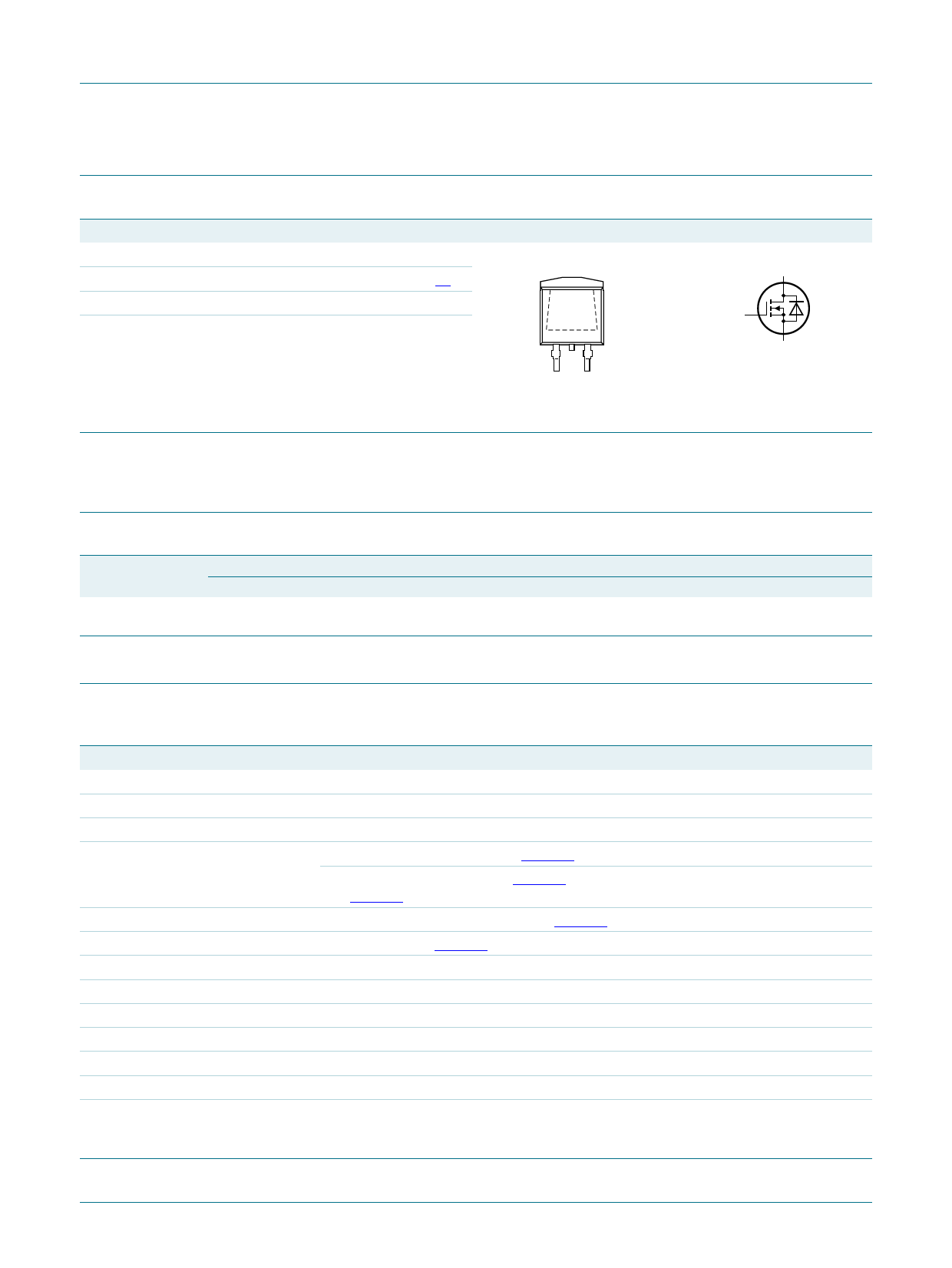

2. Pinning information

Table 2. Pinning information

Pin

Symbol Description

1

G

gate

2

D

drain

3

S

source

mb

D

mounting base; connected to

drain

Simplified outline

mb

[1]

2

13

SOT404

(D2PAK)

[1] It is not possible to make a connection to pin 2.

3. Ordering information

Graphic symbol

D

G

mbb076 S

Table 3. Ordering information

Type number

Package

Name

Description

PHB101NQ04T D2PAK

plastic single-ended surface-mounted package (D2PAK); 3 leads (one

lead cropped)

Version

SOT404

4. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter

Conditions

VDS

VDGR

VGS

ID

drain-source voltage

drain-gate voltage

gate-source voltage

drain current

Tj ≥ 25 °C; Tj ≤ 175 °C

Tj ≥ 25 °C; Tj ≤ 175 °C; RGS = 20 kΩ

VGS = 10 V; Tmb = 100 °C; see Figure 1

VGS = 10 V; Tmb = 25 °C; see Figure 1;

see Figure 3

IDM

peak drain current

Ptot

total power dissipation

Tstg

storage temperature

Tj

junction temperature

Source-drain diode

tp ≤ 10 µs; pulsed; Tmb = 25 °C; see Figure 3

Tmb = 25 °C; see Figure 2

IS

source current

ISM

peak source current

Avalanche ruggedness

Tmb = 25 °C

tp ≤ 10 µs; pulsed; Tmb = 25 °C

EDS(AL)S

non-repetitive

VGS = 10 V; Tj(init) = 25 °C; ID = 45 A; Vsup ≤ 55 V;

drain-source avalanche unclamped; tp = 0.17 ms; RGS = 50 Ω

energy

Min Max Unit

-

40

V

-

40

V

-20 20

V

-

71

A

-

75

A

-

240 A

-

157 W

-55 175 °C

-55 175 °C

-

75

A

-

240 A

-

200 mJ

PHB101NQ04T_2

Product data sheet

Rev. 02 — 10 March 2009

© NXP B.V. 2009. All rights reserved.

2 of 12