ISP1563 Просмотр технического описания (PDF) - Philips Electronics

Номер в каталоге

Компоненты Описание

Список матч

ISP1563 Datasheet PDF : 107 Pages

| |||

Philips Semiconductors

ISP1563

HS USB PCI Host Controller

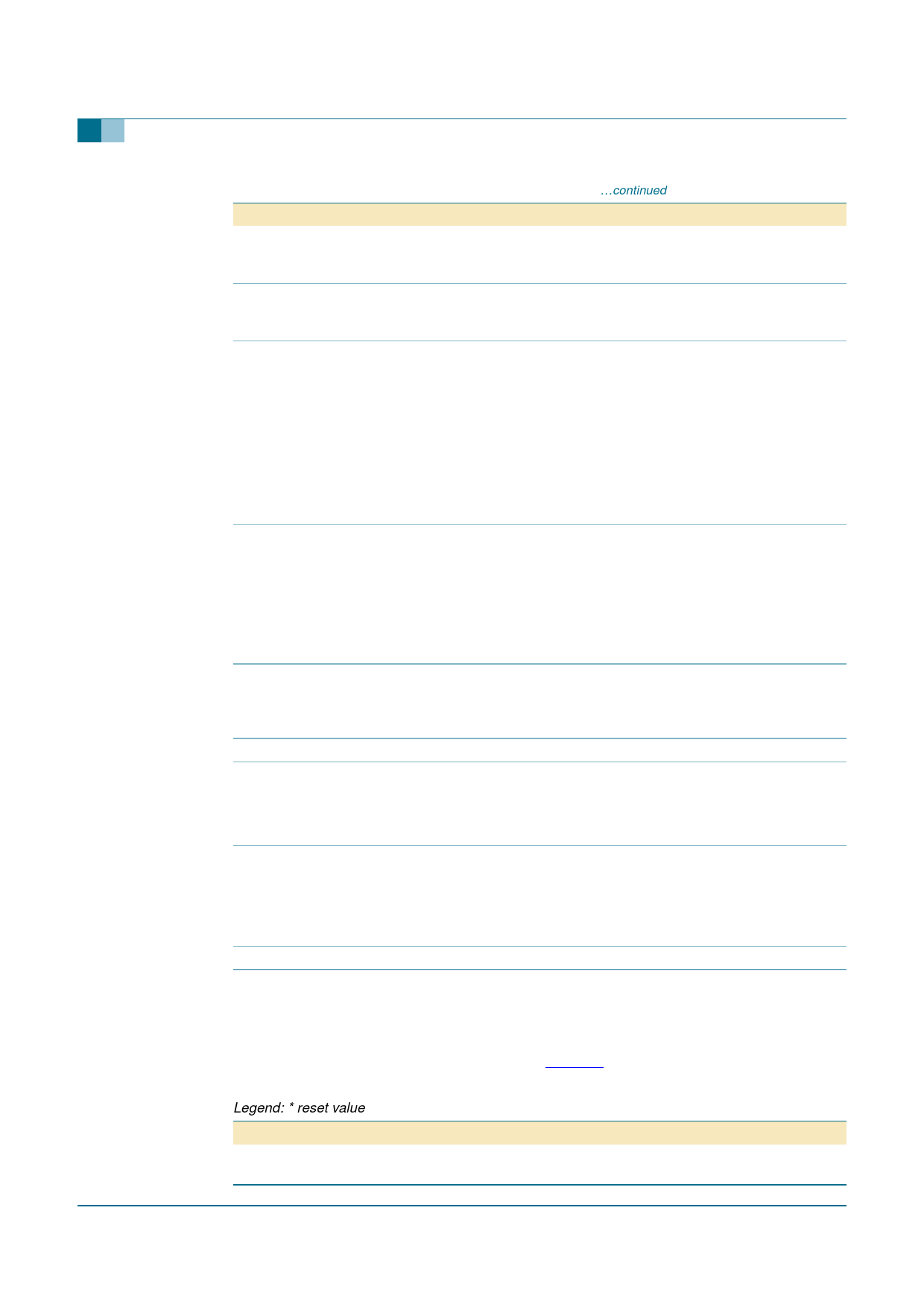

Table 9: Status register (address 06h) bit description…continued

Bit Symbol Description

12

RTA

Received Target Abort: This bit must be set by a master device whenever its

transaction is terminated with Target-Abort. All master devices must

implement this bit.

11

STA

Signaled Target Abort: This bit must be set by a target device whenever it

terminates a transaction with Target-Abort. Devices that never signal

Target-Abort do not need to implement this bit.

10 to 9 DEVSELT DEVSEL Timing: These bits encode the timing of DEVSEL#. There are three

[1:0]

allowable timing to assert DEVSEL#:

00b — Fast

01b — Medium

10b — Slow

11b — Reserved.

These bits are read-only and must indicate the slowest time that a device

asserts DEVSEL# for any bus command, except Configuration Read and

Configuration Write.

8

MDPE Master Data Parity Error: This bit is implemented by bus masters. It is set

when the following three conditions are met:

• The bus agent asserted PERR# itself, on a read; or observed PERR#

asserted, on a write.

• The agent setting the bit acted as the bus master for the operation in

which error occurred.

• PER (bit 6 in the Command register) is set.

7

FBBC Fast Back-to-Back Capable: This read-only bit indicates whether the target

is capable of accepting fast back-to-back transactions when the transactions

are not to the same agent. This bit can be set to logic 1, if the device can

accept these transactions; and must be set to logic 0 otherwise.

6

reserved -

5

66MC 66 MHz Capable: This read-only bit indicates whether this device is capable

of running at 66 MHz.

0 — 33 MHz

1 — 66 MHz.

4

CL

Capabilities List: This read-only bit indicates whether this device implements

the pointer for a new capabilities linked list at offset 34h.

0 — No new capabilities linked list is available

1 — The value read at offset 34h is a pointer in configuration space to a linked

list of new capabilities.

3 to 0 reserved -

8.2.1.5 Revision ID register

This 1 B read-only register indicates a device-specific revision identifier. The value is

chosen by the vendor. This field is a vendor-defined extension of the Device ID. The

Revision ID register bit description is given in Table 10.

Table 10: REVID - Revision ID register (address 08h) bit description

Legend: * reset value

Bit Symbol

Access Value Description

7 to 0 REVID[7:0] R

11h*

Revision ID: This byte specifies the design revision

number of functions.

9397 750 14224

Product data sheet

Rev. 01 — 14 July 2005

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

20 of 107