8405202QA Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

Список матч

8405202QA Datasheet PDF : 37 Pages

| |||

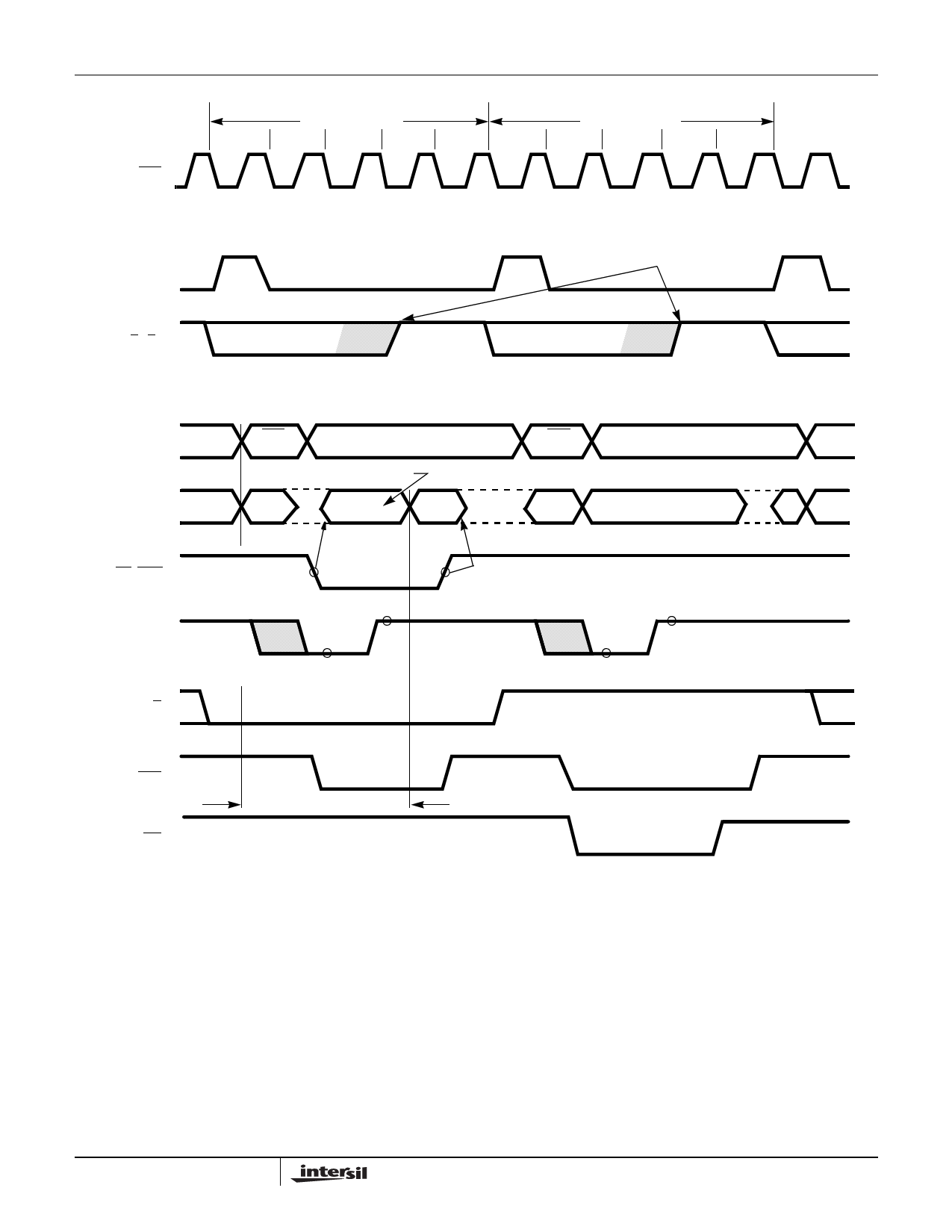

CLK

ALE

S2-S0

80C86

(4 + NWAIT) = TCY

(4 + NWAIT) = TCY

t1

t2

t3

tWAIT

t4

t1

t2

t3

tWAIT t4

GOES INACTIVE IN THE STATE

JUST PRIOR TO t4

ADDR/

STATUS

ADDR/DATA

RD, INTA

READY

DT/R

BHE,

A19-A16

A15-A0

S7-S3

BUS RESERVED

FOR DATA IN

D15-D0

VALID

BHE

A19-A16

S7-S3

A15-A0

DATA OUT (D15-D0)

READY

WAIT

READY

WAIT

DEN

WR

MEMORY ACCESS TIME

FIGURE 3. BASIC SYSTEM TIMING

External Interface

Processor RESET and Initialization

Processor initialization or start up is accomplished with

activation (HIGH) of the RESET pin. The 80C86 RESET is

required to be HIGH for greater than 4 CLK cycles. The 80C86

will terminate operations on the high-going edge of RESET and

will remain dormant as long as RESET is HIGH. The low-going

transition of RESET triggers an internal reset sequence for

approximately 7 CLK cycles. After this interval, the 80C86

operates normally beginning with the instruction in absolute

location FFFF0H (see Figure 2). The RESET input is internally

synchronized to the processor clock. At initialization, the

HIGH-to-LOW transition of RESET must occur no sooner than

50µs (or 4 CLK cycles, whichever is greater) after power-up, to

allow complete initialization of the 80C86.

NMl will not be recognized prior to the second CLK cycle

following the end of RESET. If NMl is asserted sooner than nine

clock cycles after the end of RESET, the processor may

execute one instruction before responding to the interrupt.

12

FN2957.3

January 9, 2009