8405202QA Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

Список матч

8405202QA Datasheet PDF : 37 Pages

| |||

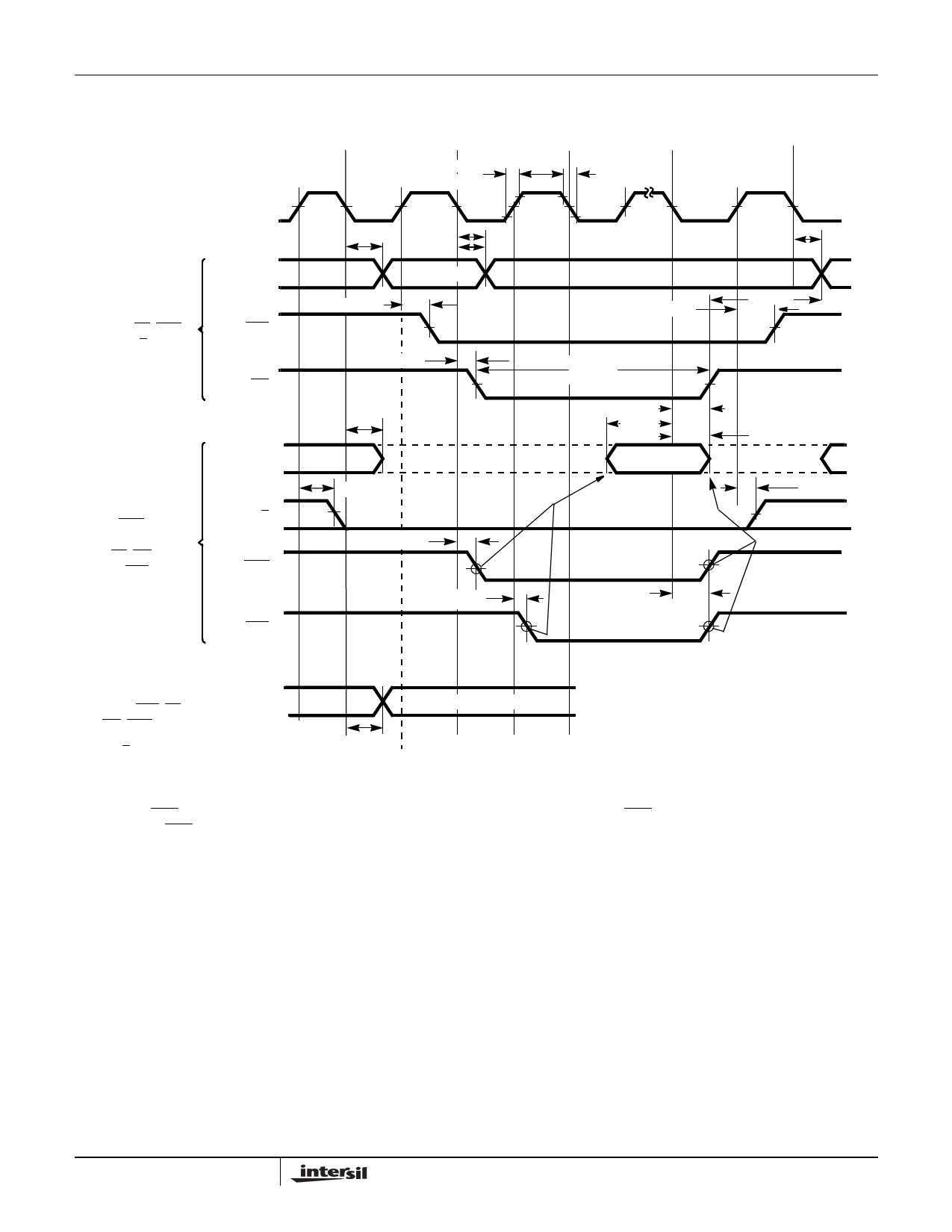

Waveforms (Continued)

80C86

CLK (82C84A OUTPUT)

AD15-AD0

WRITE CYCLE

(RD, INTA,

DT/R = VOH)

DEN

WR

AD15-AD0

INTA CYCLE

(SEE NOTE)

(RD, WR = VOH

BHE = VOL)

DT/R

INTA

DEN

t1

t2

(4)

TCH1CH2

(17)

TCLAV

(26)

TCLDV

TCLAX

(18)

AD15-AD0

TCVCTV (29)

(29) TCVCTV

(19)

TCLAZ

TCHCTV

(30)

(29) TCVCTV

(29) TCVCTV

t3

tW

(5)

TCL2CL1

TW

t4

(27)

TCLDX2

DATA OUT

(31) TCVCTX

TWHDX

(28)

(38)

TWLWH

TCVCTX (31)

TDVCL (6)

POINTER

TCLDX1 (7)

TCHCTV (30)

TCVCTX

(31)

SOFTWARE

HALT -

DEN, RD,

WR, INTA = VOH

AD15-AD0

DT/R = INDETERMINATE

TCLAV

(17)

INVALID ADDRESS

SOFTWARE HALT

FIGURE 7B. BUS TIMING - MINIMUM MODE SYSTEM

NOTE: Two INTA cycles run back-to-back. The 80C86 local ADDR/DATA bus is floating during both INTA cycles. Control signals are shown for the

second INTA cycle.

21

FN2957.3

January 9, 2009