T7264 Просмотр технического описания (PDF) - Agere -> LSI Corporation

Номер в каталоге

Компоненты Описание

Список матч

T7264 Datasheet PDF : 54 Pages

| |||

Data Sheet

April 1998

T7264 U-Interface 2B1Q Transceiver

Features

s U-interface 2B1Q transceiver

— Range over 18 kft on 26 AWG

— ISDN basic-rate 2B+D

— Full-duplex, 2-wire operation

— 2B1Q four-level line code

— Conforms to ANSI North American Standard

T1.601-1992

— Supports NT quiet mode and insertion loss test

mode for maintenance

s K2 interface

— 2B+D data

— 512 kbits/s TDM interface

— Frame and superframe markers

— Embedded operations channel (eoc)

— U-interface M bits and crc results

— Device control and status

s Other

— Single +5 V (±5%) supply

— –40 °C to +85 °C

— 44-pin PLCC

s Power consumption

— Operating 275 mW typical

— Idle mode 30 mW typical

s Analog front end

— On-chip line driver for 2.5 V pulses

— On-chip balance network

— Sigma-delta A/D converter

— Internal 15.36 MHz crystal oscillator

— Supports 15.36 MHz external clock input

s Digital signal processor

— Digital timing recovery (pull range ±250 ppm)

— Echo cancellation (linear and nonlinear)

— Accommodates distortion from bridged taps

— Scrambling/descrambling

— crc calculations

— Selectable LT or NT operation

— Start-up sequencing with timers

— Activation/deactivation support

— Cold start in 3.5 seconds (typical)

— Warm start in 200 ms (typical)

— U-frame formatting and decoding

Description

The Lucent Technologies Microelectronics Group

T7264 U-Interface 2B1Q Transceiver integrated cir-

cuit provides full-duplex, basic-rate (2B+D) integrated

services digital network (ISDN) communications on a

2-wire digital subscriber loop at either the LT or NT

and conforms to the ANSI North American Standard

T1.601-1992. The single +5 V CMOS device is pack-

aged in a 44-pin plastic leaded chip carrier (PLCC).

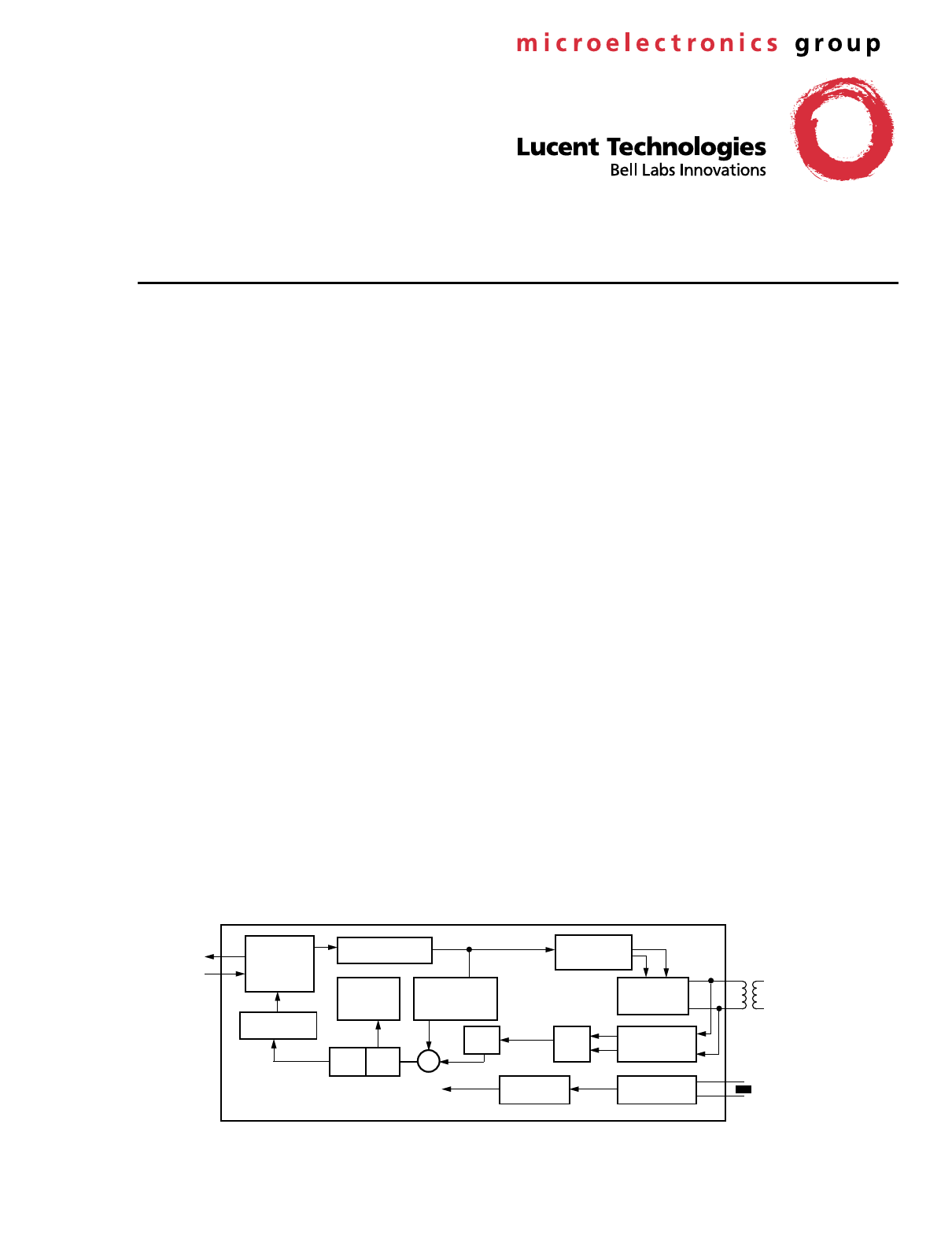

K2 BUS

SCRAMBLER

K2

FORMAT,

DECODE

SIGNAL

ECHO

DETECT CANCELER

DESCRAM.

DFE AGC

– + DEC

∑

2B1Q

ENCODER

LINE

DRIVER

A/D

BALANCE

NETWORK

T7264

DIG. PLL

XTAL OSC.

Figure 1. T7264 Simplified Block Diagram

2-WIRE

2B1Q

U-INTERFACE

15.36 MHz

5-5161