PHP225 Просмотр технического описания (PDF) - NXP Semiconductors.

Номер в каталоге

Компоненты Описание

Список матч

PHP225 Datasheet PDF : 12 Pages

| |||

Nexperia

PHP225

Dual P-channel intermediate level FET

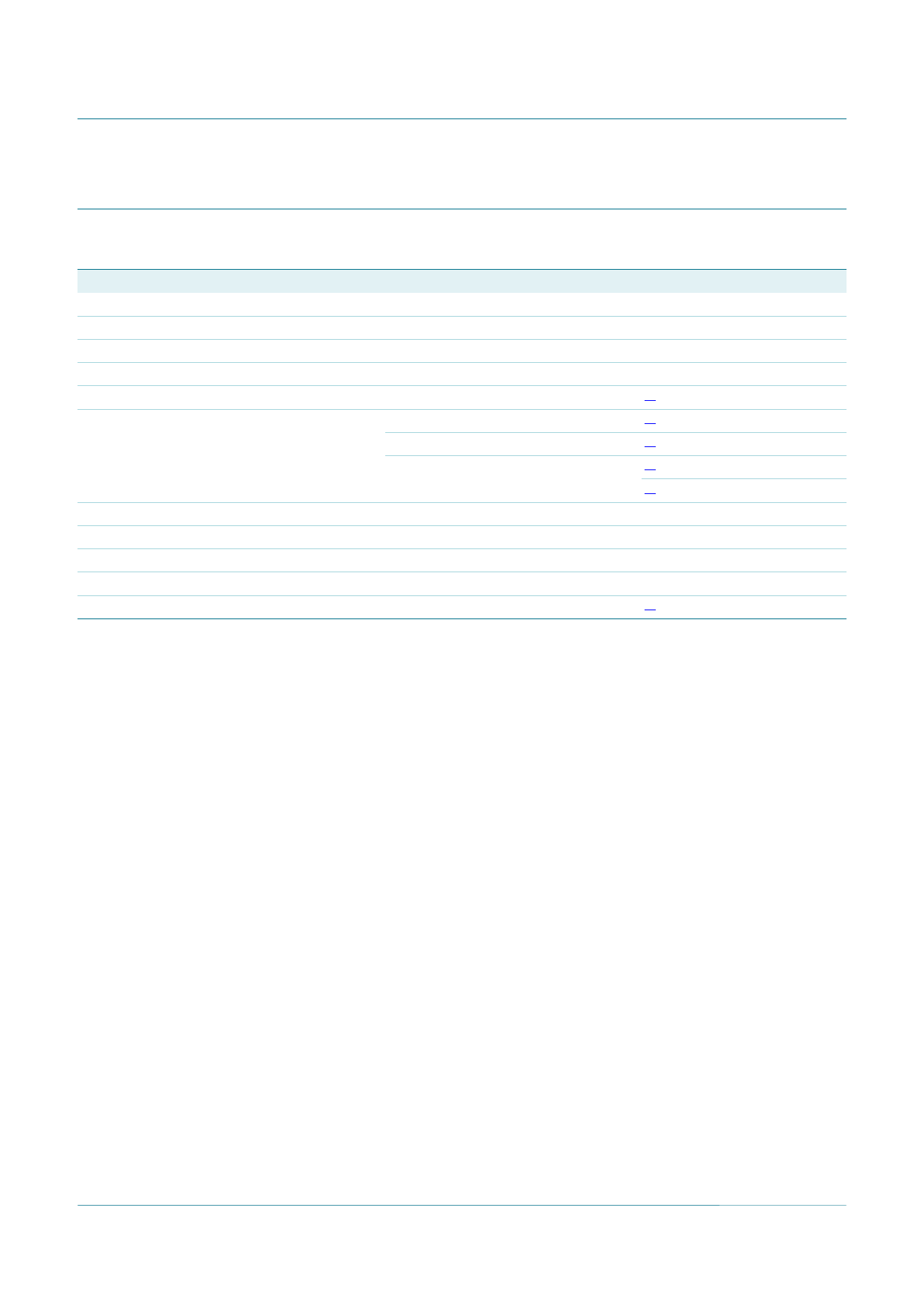

4. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol

Parameter

Conditions

VDS

VGS

VGSO

ID

IDM

Ptot

drain-source voltage

gate-source voltage

gate-source voltage

drain current

peak drain current

total power dissipation

Tj ≥ 25 °C; Tj ≤ 150 °C

open drain

Tsp ≤ 80 °C

Tsp = 25 °C; pulsed

Tamb = 25 °C

Tsp = 80 °C

Tamb = 25 °C

Tstg

storage temperature

Tj

junction temperature

Source-drain diode

IS

source current

ISM

peak source current

Tsp ≤ 80 °C

Tsp = 25 °C; pulsed

Min Max Unit

-

-30 V

-

-

V

-20 20 V

-

-2.3 A

[1]

-

-10 A

[2]

-

1

W

[3]

-

2

W

[4]

-

1.3 W

[5]

-

2

W

-65 150 °C

-

150 °C

-

[1]

-

-1.25 A

-5

A

[1] Pulse width and duty cycle limited by maximum junction temperature.

[2] Maximum permissible dissipation per MOS transistor. Device mounted on printed-circuit board with a thermal resistance from ambient to

tie-point of 90 K/W.

[3] Maximum permissible dissipation per MOS transistor. Both devices may be loaded up to 2 W at the same time.

[4] Maximum permissible dissipation if only one MOS transistor dissipates. Device mounted on printed-circuit board with a thermal

resistance from ambient to tie-point of 90 K/W.

[5] Maximum permissible dissipation per MOS transistor. Device mounted on printed-circuit board with a thermal resistance from ambient to

tie-point of 27.5 K/W.

PHP225

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 04 — 17 March 2011

© Nexperia B.V. 2017. All rights reserved

3 of 12