AK4523VF Просмотр технического описания (PDF) - Asahi Kasei Microdevices

Номер в каталоге

Компоненты Описание

Список матч

AK4523VF Datasheet PDF : 20 Pages

| |||

ASAHI KASEI

[AK4523]

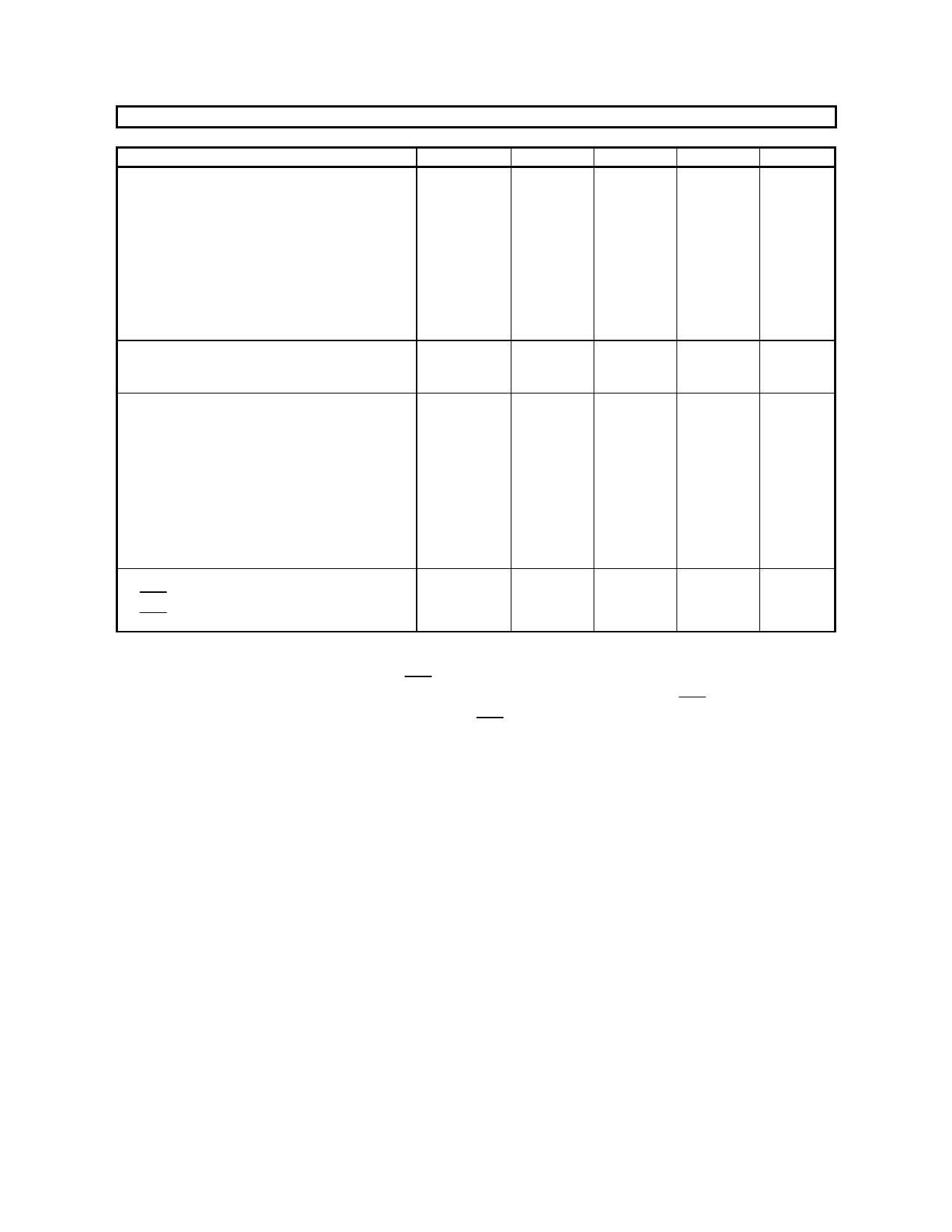

SWITCHING CHARACTERISTICS

(Ta=25°C; VA=4.5 ~ 5.5V; VD=3.0 ~ 5.5V; CL=20pF)

Parameter

Symbol

min

typ

Master Clock Timing

256fs:

Pulse Width Low

Pulse Width High

384fs:

Pulse Width Low

Pulse Width High

512fs:

Pulse Width Low

Pulse Width High

fCLK

tCLKL

tCLKH

fCLK

tCLKL

tCLKH

fCLK

tCLKL

tCLKH

4.096

27

27

6.144

20

20

8.192

15

15

LRCK Timing

Frequency

Duty Cycle

fs

16

dfs

45

Serial Interface Timing

SCLK Period

tSCK

320

SCLK Pulse Width Low

tSCKL

65

Pulse Width High

tSCKH

65

LRCK Edge to SCLK “”

(Note 14)

tLRS

45

SCLK “” to LRCK Edge

(Note 14)

tSLR

45

LRCK to SDTO (MSB)

tLRM

SCLK “¯” to SDTO

SDTI Hold Time

SDTI Setup Time

tSSD

tSDH

40

tSDS

25

Reset Timing

PD Pulse Width

(Note 15)

tPD

150

PD “” to SDTO valid

(Note 16)

tPDV

516

max

12.288

18.432

24.576

48

55

40

70

Note 14. SCLK rising edge must not occur at the same time as LRCK edge.

15. The AK4523 can be reset by bringing PD “L”.

When the state of CMODE change during operation, the AK4523 should be reset by PD .

16. These cycles are the number of LRCK rising from PD rising.

Units

MHz

ns

ns

MHz

ns

ns

MHz

ns

ns

kHz

%

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

1/fs

M0021-E-03

-8-

1999/12