AK4523VF Просмотр технического описания (PDF) - Asahi Kasei Microdevices

Номер в каталоге

Компоненты Описание

Список матч

AK4523VF Datasheet PDF : 20 Pages

| |||

ASAHI KASEI

[AK4523]

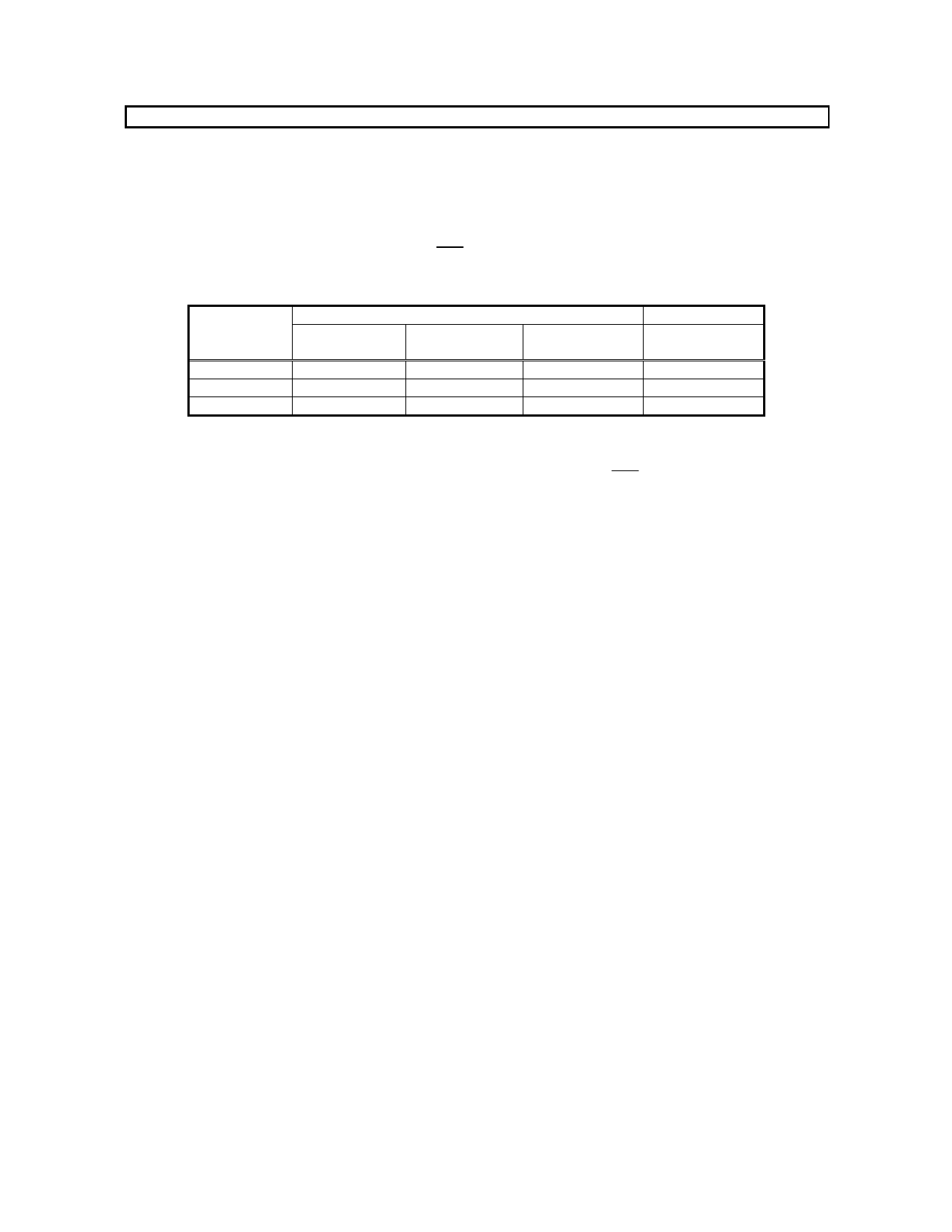

n System Clock

OPERATION OVERVIEW

The master clock (MCLK) can be external clock input to the MCKI pin. CMODE is used to select either MCLK=256fs,

384fs or 512fs. The relationship between the MCLK and the desired sample rate is defined in Table 1. The LRCK clock

input must be synchronized with MCLK, however the phase is not critical. Internal timing is synchronized to LRCK upon

power-up. All external clocks must be present unless PD = “L”, otherwise excessive current may result from abnormal

operation of internal dynamic logic.

fs

32.0kHz

44.1kHz

48.0kHz

256fs

CMODE = “L”

8.1920MHz

11.2896MHz

12.2880MHz

MCLK

384fs

CMODE = “H”

12.2880MHz

16.9344MHz

18.4320MHz

512fs

CMODE = “NC”

16.384MHz

22.579MHz

24.576MHz

SCLK

64fs

2.048MHz

2.822MHz

3.072MHz

Table 1. System Clock Example

When the state of CMODE change under operation, the AK4523 should be reset by PD . At that case, the analog outputs

should be muted externally because some click noise may occur.

M0021-E-03

- 10 -

1999/12