RT5370N Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

Список матч

RT5370N Datasheet PDF : 70 Pages

| |||

RT5370

Datasheet

Revision August 30, 2010

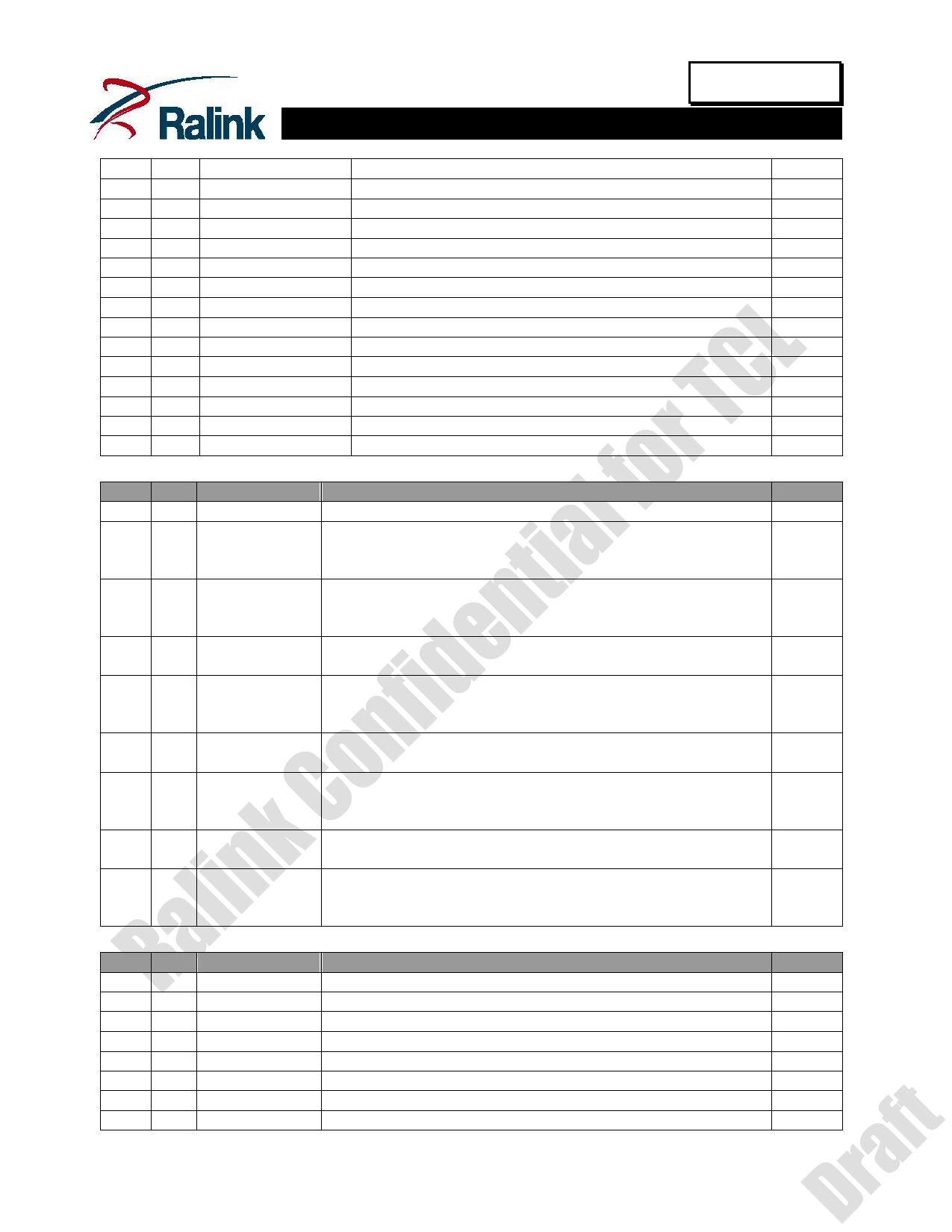

14 R/W MAC_INT3_EN

MAC interrupt 3: Auto wakeup interrupt

0

13 R/W MAC_INT2_EN

MAC interrupt 2: TX status interrupt

0

12 R/W MAC_INT1_EN

MAC interrupt 1: Pre-TBTT interrupt

0

11 R/W MAC_INT0_EN

MAC interrupt 0: TBTT interrupt

0

10

Reserved

9

R/W MCU_CMD_INT_MSK MCU command interrupt enable

0

8

R/W TX_DONE_INT_MSK5 TX Queue#5 packet transmit interrupt

0

7

R/W TX_DONE_INT_MSK4 TX Queue#4 packet transmit interrupt

0

6

R/W TX_DONE_INT_MSK 3 TX Queue#3 packet transmit interrupt

0

5

R/W TX_DONE_INT_MSK 2 TX Queue#2 packet transmit interrupt

0

4

R/W TX_DONE_INT_MSK 1 TX Queue#1 packet transmit interrupt

0

3

R/W TX_DONE_INT_MSK 0 TX Queue#0 packet transmit interrupt

0

2

R/W RX_DONE_INT_MSK RX packet receive interrupt

0

1

R/W TX_DLY_INT_MSK Summary of the whole WPDMA TX related interrupts

0

0

R/W RX_ DLY_INT_MSK Summary of the whole WPDMA RX related interrupts

0

WPDMA_GLO_CFG (offset:0x0208,default :0x00000060)

Bits Type Name

Description

Init Value

31:16

Reserved

15:8 R/W HDR_SEG_LEN Specify the header segment size in byte to support RX header/payload 8’b0

scattering function, when set to a non-zero value.

When set to zero, the header/payload scattering feature is disabled.

7

R/W BIG_ENDIAN

The endian mode selection. DMA applies the endian rule to convert 0

payload and TX/RX information. DMA won’t apply endian rule to

register or descriptor. 1: big endian. 0: little endian.

6

R/W TX_WB_DDONE 0 :Disable TX_DMA writing back DDONE into TXD

1’b1

1 : Enable TX_DMA writing back DDONE into TXD

5:4 R/W WPDMA_BT_SIZE Define the burst size of WPDMA

2’d2

0 : 4 DWORD (16bytes)

1 : 8 DWORD (32 bytes)

2 : 16 DWORD (64 bytes) 3 : 32 DWORD (128 bytes)

3

RO RX_DMA_BUSY 1 : RX_DMA is busy

0

0 : RX_DMA is not busy

2

R/W RX_DMA_EN

1 : Enable RX_DMA

0

0 : Disable RX_DMA (when disabled, RX_DMA will finish the current

receiving packet, then stop.)

1

RO TX_DMA_BUSY 1 : TX_DMA is busy

0

0 : TX_DMA is not busy

0

R/W TX_DMA_EN

1 : Enable TX_DMA

0

0 : Disable TX_DMA (when disabled, TX_DMA will finish the current

sending packet, then stop.)

WPDMA_RST_IDX (offset:0x020C,default :0x00000000)

Bits Type Name

Description

31:17

Reserved

16 W1C RST_DRX_IDX0 Write 1 to reset to RX_DMARX_IDX0 to 0

15:6

Reserved

5

W1C RST_DTX_IDX5 Write 1 to reset to TX_DMATX_IDX5 to 0

4

W1C RST_DTX_IDX4 Write 1 to reset to TX_DMATX_IDX4 to 0

3

W1C RST_DTX_IDX3 Write 1 to reset to TX_DMATX_IDX3 to 0

2

W1C RST_DTX_IDX2 Write 1 to reset to TX_DMATX_IDX2 to 0

1

W1C RST_DTX_IDX1 Write 1 to reset to TX_DMATX_IDX1 to 0

DSRT5370_ V1. 0_083010

Form No.:QS-073-F02

Rev.:1

Kept by: DCC

Init Value

1’b0

1’b0

1’b0

1’b0

1’b0

1’b0

-8-

Ret. Time: 5 Years

Draft