ZR36050 Просмотр технического описания (PDF) - Zoran Corporation

Номер в каталоге

Компоненты Описание

Список матч

ZR36050 Datasheet PDF : 52 Pages

| |||

ADVANCE INFORMATION

ZR36050

Compressed Data Interface

When the MSTR bit of the HARDWARE register is set, the

ZR36050 transfers compressed data using the Compressed

Data Interface, directly accessing the external compressed data

memory in a Master mode. Data transfers are 8 bits wide, using

the CODE bus and the control signals CCS, COE, CWE, and

CAEN.

The CBUSY input can be used by the external compressed data

memory control logic, to suppress read or write access by the

Compressed Data Interface when the memory is temporarily

unavailable. CBUSY is sampled one CLK_IN prior to the begin-

ning of a bus cycle, and its state determines whether the bus

cycle is executed or suppressed.

The Compressed Data Interface does not provide the address

signals to the compressed data memory. The memory must

appear to the interface as a FIFO. CAEN, which is activated on

each access, can be used by the memory control logic to enable

an address counter.

The cycle time of master mode transfers can be from one to eight

CLK_IN cycles, and is specified by the CFIS field of the

HARDWARE register. A new bus cycle can begin immediately

after the end of the previous cycle.

A bus cycle starts when the Compressed Data Interface acti-

vates CCS. CCS is stable throughout the bus cycle, and CAEN

is active during the last CLK_IN cycle of the bus cycle. In back-

to-back bus cycles, CCS is active continuously.

In a read cycle, executed during decoding, COE goes active 0.5

x CLK_IN after the beginning of the cycle, and remains active

until the end of the cycle. The memory must drive data on the

CODE bus while COE is active. The Compressed Data Interface

latches the data on the trailing edge of COE.

In a write cycle, executed during encoding, CWE goes active 0.5

x CLK_IN after the beginning of the cycle, and remains active

until the end of the cycle. The Compressed Data Interface drives

CODE with valid data for the duration of the bus cycle.

When the Compressed Data Interface is inactive, the CODE bus

floats, and is pulled low by the internal pull-down devices. The

interface control signals are driven high.

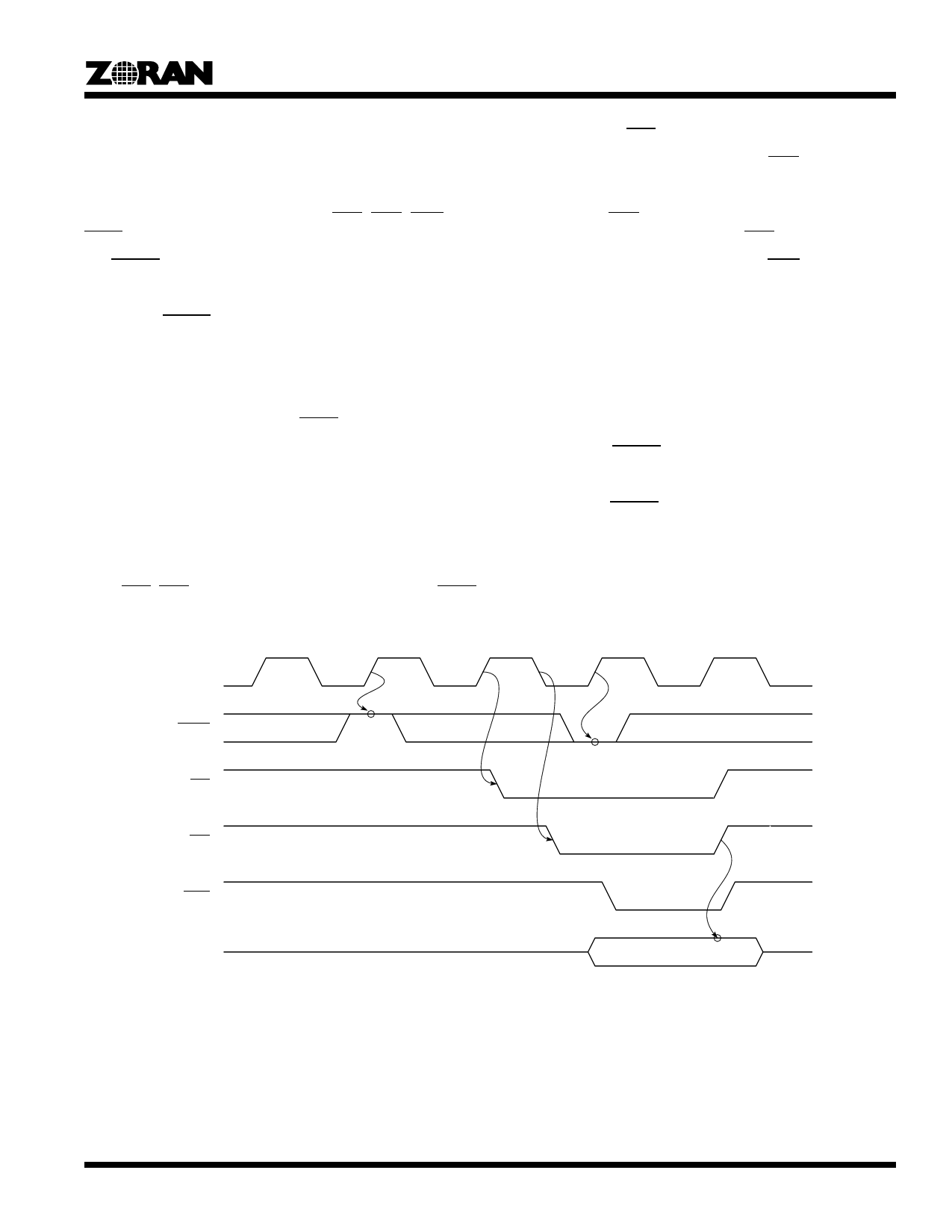

Figure 15 and Figure 16 show examples of read and write

cycles, with CFIS = 001 (2 CLK_IN cycles per bus cycle). In

these examples, CBUSY is sampled first inactive, to enable a

bus cycle, then active to suppress the start of the next bus cycle.

The dashed lines depict the start of a bus cycle that could have

been executed if CBUSY had been sampled active.

CLK_IN

CBUSY

CCS

COE

CAEN

CODE

Figure 15. Master Mode Compressed Data Read in Decoding, Shown for Bus Cycle Time of Two CLK_IN

21