GF9101-CMQ Просмотр технического описания (PDF) - Gennum -> Semtech

Номер в каталоге

Компоненты Описание

Список матч

GF9101-CMQ Datasheet PDF : 23 Pages

| |||

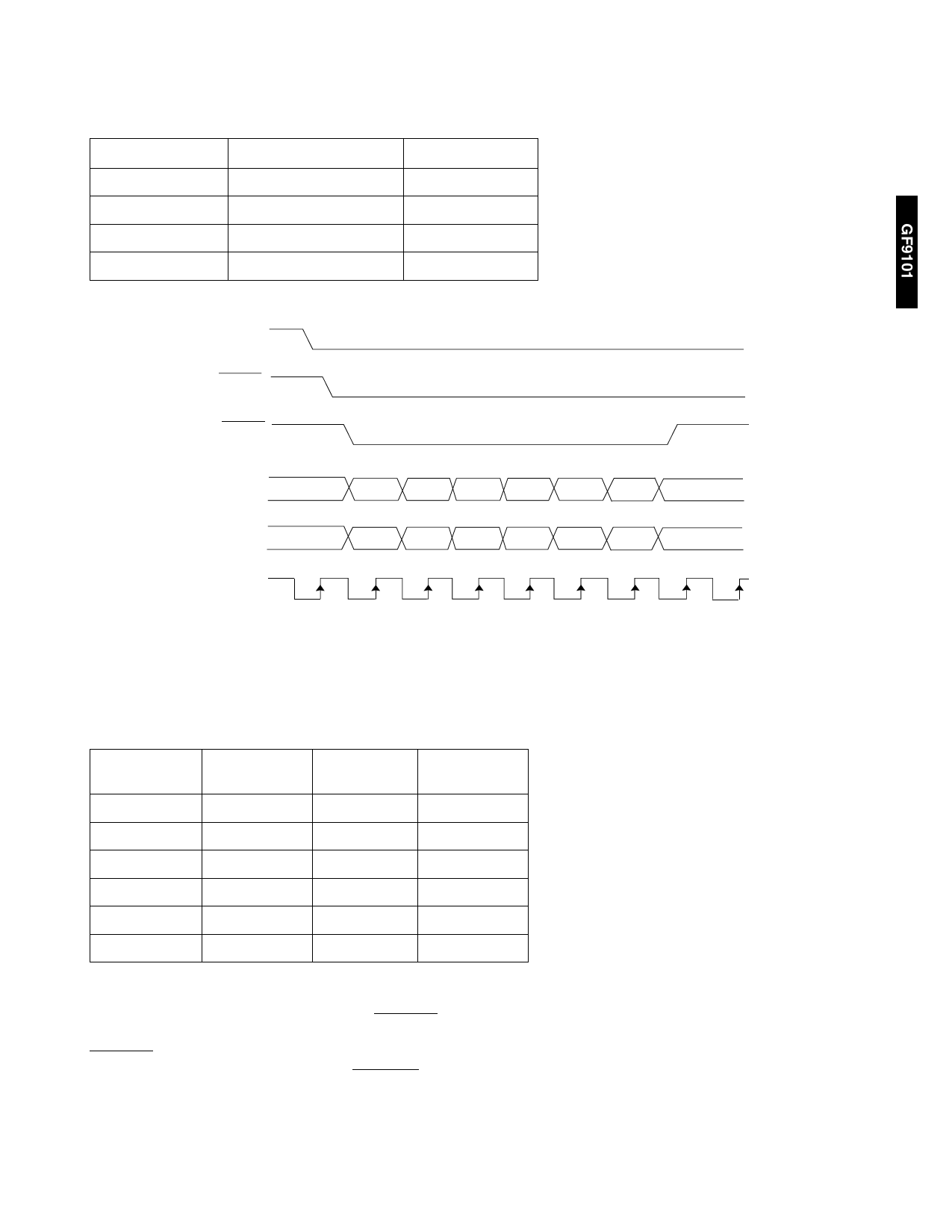

The timing diagram shown in Figure 1 loads the memories shown in Table 4:

TABLE 4: Memory Loaded into Internal RAM in Parallel Load Mode

TAP (location)

12-bit WORD IN HEX.

MEMORY BANK

1 (0)

FB2

MB0

2 (0)

EF4

MB0

11 (107)

CCC

MB5

12 (107)

DDD

MB5

CONFIGURE

LOAD_EN

COEF_WR

COEF_DATA

(7-0)

COEF_ADDR

(9-0)

XX

F4

2E

FB

DD

CD

CC

XX

XX

300

380

000

36B

3EB

2EB

XX

CLK_IN

Fig. 1 Parallel Loading Timing Diagram

The address generated is shown in Table 5.

Timing for the parallel loading signals is the same as that

for other synchronous inputs.

TABLE 5: Address Generation for Parallel Loading Example

DESTINATION

COEF_ADDR

(9-7) IN BINARY

COEF_ADDR

(6-0) IN HEX

COEF_ADDR

(9-0) IN HEX

TEMP_REG_A

110

X

300

TEMP_REG_B

111

X

380

MB0

000

0

000

TEMP_REG_A

110

X

36B or 300

TEMP_REG_B

111

X

3EB or 380

MB5

101

6B

2EB

MICROPROCESSOR LOADING

If microprocessor loading is selected, the LOAD_EN pin

alone determines the run mode or the load mode. When

LOAD_EN is low, the load mode is selected, the run mode

is disabled, but a write will not occur until COEF_WR is low.

Microprocessor loading is random access and

asynchronous. Like parallel loading, microprocessor

loading uses COEF_DATA (7-0) and COEF_ADDR (9-0) to

write three 8-bit words for each 24-bit memory written.

Addressing is the same as for parallel loading. In

microprocessor mode, at least one set of filter coefficients

5

520 - 64 - 7