GF9101-CMQ Просмотр технического описания (PDF) - Gennum -> Semtech

Номер в каталоге

Компоненты Описание

Список матч

GF9101-CMQ Datasheet PDF : 23 Pages

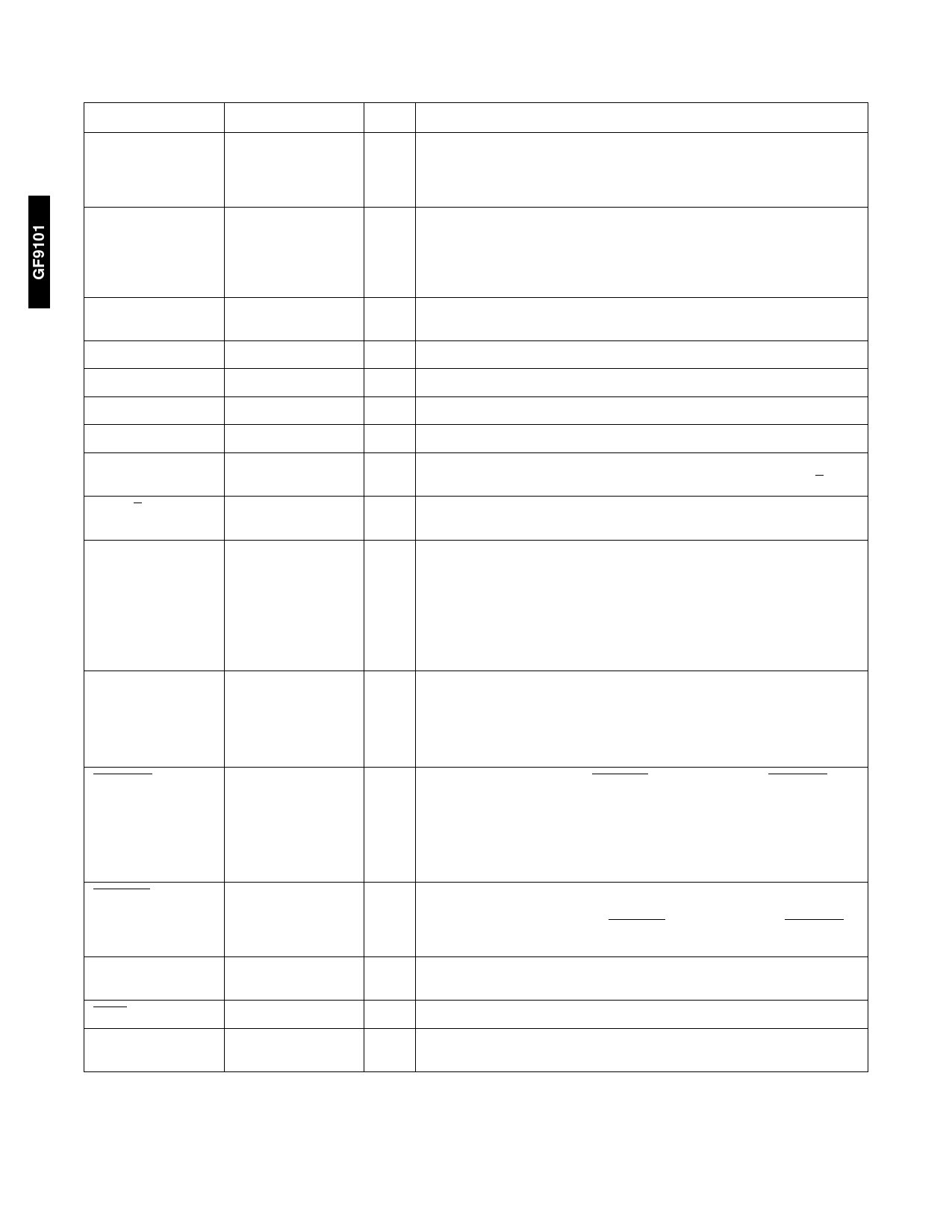

| |||

I/O DESCRIPTION

SYMBOL

VDD

GND

CLK_IN

DATA_A_IN (9-0)

DATA_B_IN (9-0)

ENA

ENB

ENC

SEL_A/B

COEF_DATA (7-0)

COEF_ADDR (9-0)

COEF_WR

LOAD_EN

NEGATE

ZERO

FB_SEL

PIN NO.

1, 10, 20, 29, 40, 41,

59, 69, 80, 81, 90, 99,

109, 120, 121, 129,

140, 150, 160

3, 6, 8, 19, 33, 36, 39,

46, 49, 60, 73, 76, 79,

83, 86, 88, 100, 113,

116, 119, 122, 125,

139, 153, 155, 159

138

127, 128, 130-137

141-149, 151

23

24

25

22

96-98, 101-105

78, 77, 75, 74, 72, 47,

45-42

17

18

126

123

124

TYPE

DESCRIPTION

+5 V power supply pins. 0.1µF capacitors between the VCC and GND pins

are recommended.

Device ground.

I

System clock. All inputs except for CONFIGURE, and all internal registers are

clocked on the rising edge of CLK_IN.

I

Input data to registers A0 - A11. 9 bit signed or 10 bit unsigned data.

I

Input data to registers B11 - B0. 9 bit signed or 10 bit unsigned data.

I

Shift enable for A0 - A11. Enables shifting of A registers when high.

I

Shift enable for B0 - B11. Enables shifting of B registers when high.

I

Enable for C0-C11. Enables C registers when high. The C registers transfer

data from either the A or B registers depending on the state of SEL_A/B.

I

Selects A or B registers. Selects registers A when high or registers B when

low to be transferred to the C registers.

I

Data bus for coefficients and configuration register:

a) Parallel and microprocessor loading modes : COEF_DATA (7-0) is used to

load 8 bit data into internal RAM.

b) Serial Loading mode: COEF_DATA (7) is used to serially load the internal

RAM.

c) Configuration mode: COEF_DATA (6-0) are inputs to the CONFIGURATION

register.

I

Address bus for internal RAM (address 0 —> 107):

a) Run mode: COEF_ADDR (6-0) selects one of the 108 sets of 12 coefficients

in the internal RAM.

b) Parallel and micro-processor loading modes: Selects the internal RAM

address for the 8-bit data loading COEF_DATA (7-0).

I

Enable for COEF_DATA (7-0). LOAD_EN must be enabled for COEF_WR to

work:

a) Parallel and micro-processor loading modes : Enables COEF_DATA (7-0)

registers or loading 8 bit data in internal RAM.

b) Serial Loading mode: On a high to low transition, a one bit data gets

clocked in to the internal RAM through COEF_DATA bit 7.

I

Used during loading mode. This signal selects a particular GF9101 device

when 2 or more share the same bus for loading. The particular GF9101

device is selected when set low. LOAD_EN must be enabled for COEF_WR.

For a single GF9101 using the serial loading, this pin can be set low.

I

This signal negates the filter sum before it enters the pipelined output section

when high.

I

Zeros filter sum before it enters the pipelined output section when low.

I

Feedback select. Selects data in PIPELINE_IN when low or filter sum in

PIPELINE_OUT when high to the input of the output accumulator.

2

520 - 64 - 7