CDP1882 Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

Список матч

CDP1882 Datasheet PDF : 8 Pages

| |||

CDP1881C, CDP1882, CDP1882C

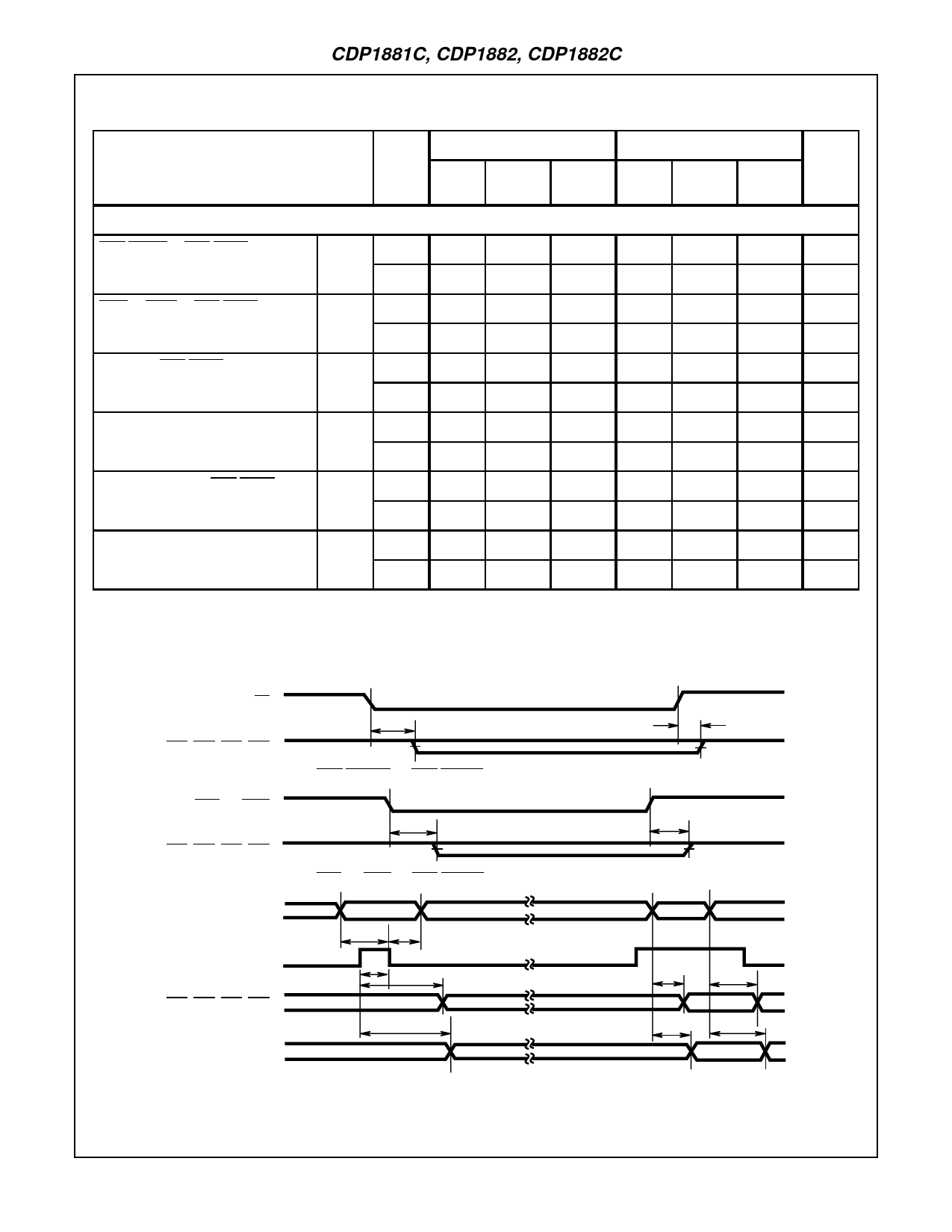

Dynamic Electrical Specifications at TA = -40oC to +85oC, VDD ± 5%, tR, tF = 20ns, VIH = 0.7 VDD, VIL = 0.3 VDD, CL = 100pF,

(See Figure 1) (Continued)

CDP1882

CDP1881C, CDP1882C

PARAMETER

VDD

(NOTE 1) (NOTE 2)

(NOTE 1) (NOTE 2)

(V)

MIN

TYP

MAX

MIN

TYP

MAX UNITS

PROPAGATION DELAY TIMES

Chip Enable to Chip Select

tCECS

5

-

10

-

75

150

-

45

100

-

75

150

ns

-

-

ns

MRD or MRW to Chip Select (Note 3) tMCS

5

-

10

-

75

150

-

40

100

-

75

150

ns

-

-

ns

CLOCK to Chip Select

tCLCS

5

-

100

175

-

100

175

ns

10

-

65

125

-

-

-

ns

CLOCK to Address

tCLA

5

-

100

175

-

100

175

ns

10

-

65

125

-

-

-

ns

Memory Address to Chip Select

tMACS

5

-

100

175

-

100

175

ns

10

-

75

125

-

-

-

ns

Memory Address to Address

tMAA

5

-

10

-

80

125

-

40

60

-

80

125

ns

-

-

ns

NOTES:

1. Typical values are for TA = 25oC.

2. Maximum limits of minimum characteristics are the values above which all devices function.

3. For CDP1881C type only.

CE

CS0, CS1, CS2, CS3

MRD OR MWR

CS0, CS1, CS2, CS3

tCECS

VALID CHIP ENABLE

(A) CHIP ENABLE TO CHIP SELECT PROPAGATION DELAY

tMCS

tMCS

(B) MRD OR MWR TO CHIP SELECT PROPAGATION DELAY (CDP1881C ONLY)

tCECS

MA0 - MA5

CLOCK

CS0, CS1, CS2, CS3

A8 - A11

tMACL

tCLCL

tCLMA

tCLCS

tCLA

(C) MEMORY ADDRESS SETUP AND HOLD TIME

FIGURE 3. TIMING WAVEFORMS

tMACS

tMAA

tMACS

tMAA

4-5