W83196S-14 Просмотр технического описания (PDF) - Winbond

Номер в каталоге

Компоненты Описание

Список матч

W83196S-14 Datasheet PDF : 15 Pages

| |||

Preliminary W83196S-14

8.0 SPECIFICATIONS

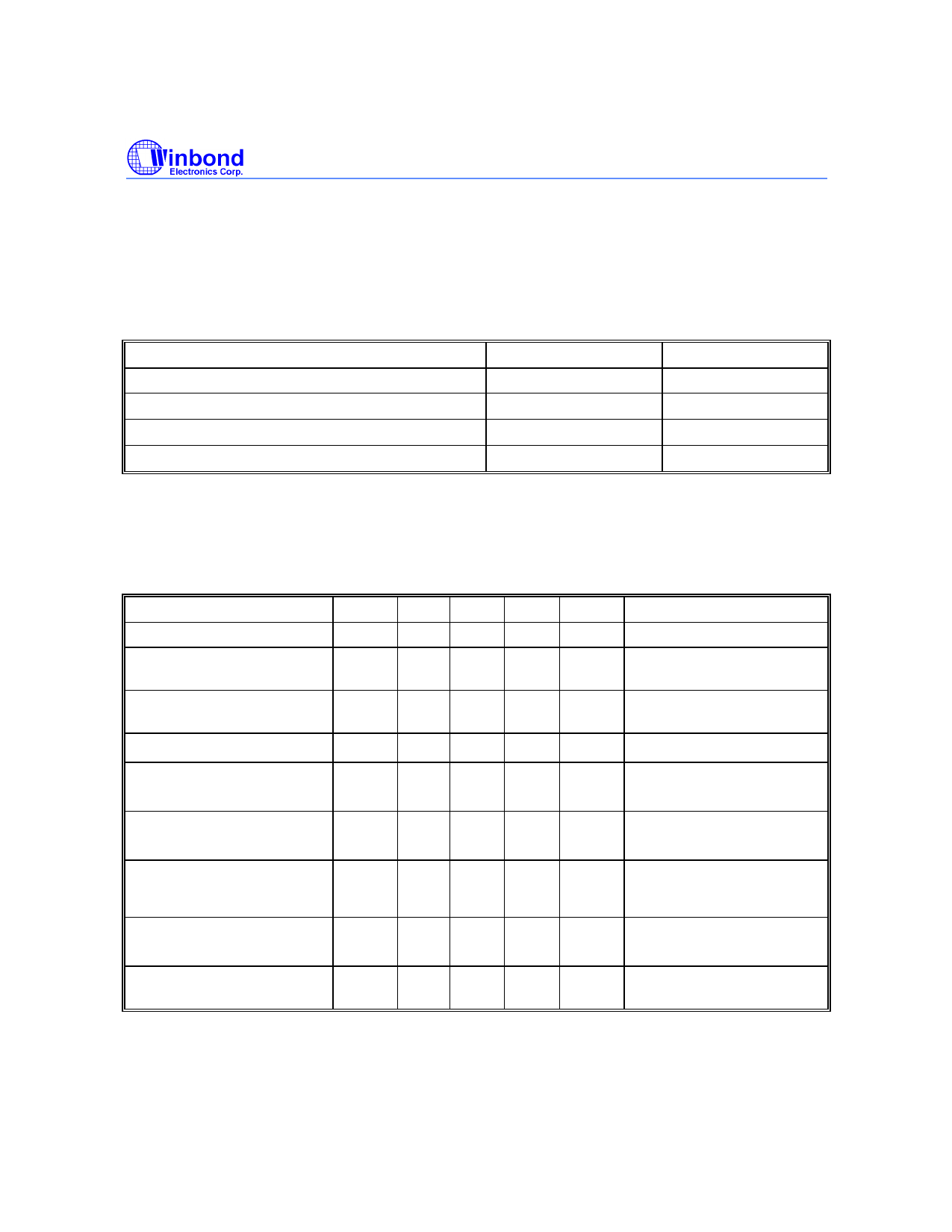

8.1 Absolute Maximum Ratings

Stresses greater than those listed in this table may cause permanent damage to the device.

Precautions should be taken to avoid application of any voltage higher than the maximum rated

voltages to this circuit. Maximum conditions for extended periods may affect reliability. Unused inputs

must always be tied to an appropriate logic voltage level (Ground or VDD).

PARAMETER

SYMBOL

RATING

Voltage on Any Pin with Respect to GND

Storage Temperature

Ambient Temperature

Operating Temperature

VDD, VIN

TSTG

TB

TA

-0.5V to +7.0V

-65° C to +150° C

-55° C to +125° C

0° C to +70° C

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the

device.

8.2 AC Characteristics

VDDR = VDDCore = VDDP = VDD4 = 3.3V ±5%, VDDA = VDDC = 2.5V ±5% , TA = 0°C to +70°C

PARAMETER

SYM. MIN. TYP. MAX. UNITS TEST CONDITIONS

Output Duty Cycle

45 50 55

% Measured at 1.5V

CPU to PCI Offset

tOFF

1

4

nS 15 pF Load Measured at

1.5V

Skew (CPU-CPU), (PCI-

PCI)

tSKEW

250 ps 15 pF Load Measured at

1.5V

Cycle to Cycle Jitter

tCCJ

CPU

tJA

Absolute Jitter

200 ps

500 ps

Jitter Spectrum 20 dB

Bandwidth from Center

BWJ

500 KHz

Output Rise (0.4V ~ 2.0V)

& Fall (2.0V ~0.4V) Time

Overshoot/Undershoot

Beyond Power Rails

tTLH

0.4

tTHL

Vover

0.7

1.6 nS 15 pF Load on CPU and

PCI outputs

1.5

V 22 Ω at source of 8 inch

PCB run to 15 pF load

Ring Back Exclusion

VRBE 0.7

2.1

V Ring Back must not enter

this range.

Publication Release Date: March 1999

-9-

Revision A1