8405202QA Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

Список матч

8405202QA Datasheet PDF : 37 Pages

| |||

80C86

AC Electrical Specifications

VCC = 5.0V ±10%TA = 0°C to +70°C (C80C86, C80C86-2)

VCC = 5.0V ±10%;TA = -55°C to +125°C (M80C86)

VCC = 5.0V ±5%;TA = -55°C to +125°C (M80C86-2). Parameters with MIN and/or MAX limits are 100%

tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are

not production tested. (Continued)

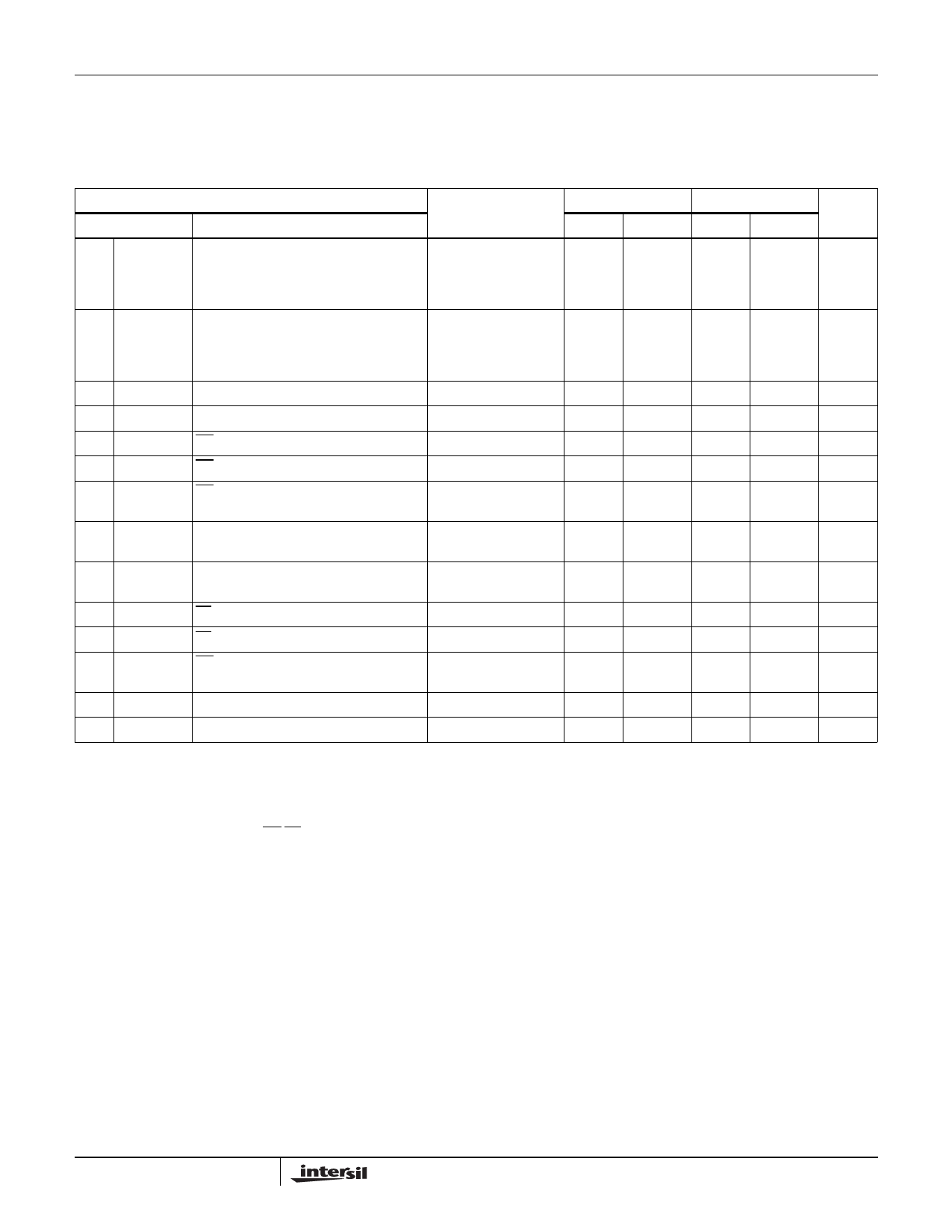

TIMING REQUIREMENTS

80C86

80C86-2

SYMBOL

PARAMETER

TEST CONDITIONS MIN

MAX

MIN

MAX UNITS

(34) TCLDX2 Data Hold Time

CL = 100pF for All

10

10

ns

80C86 Outputs (In

Addition to 80C86 Self

Load)

(35) TCVNV Control Active Delay (Note 11)

CL = 100pF for All

80C86 Outputs (In

5

45

5

45

ns

Addition to 80C86 Self

Load)

(36) TCVNX Control Inactive Delay (Note 11)

(37) TAZRL Address Float to Read Active

(38) TCLRL RD Active Delay

(39) TCLRH RD Inactive Delay

(40) TRHAV RD Inactive to Next Address Active

CL = 100pF

CL = 100pF

CL = 100pF

CL = 100pF

CL = 100pF

10

45

10

45

ns

0

0

ns

10

165

10

100

ns

10

150

10

80

ns

TCLCL

TCLCL

ns

- 45

- 40

(41) TCHDTL Direction Control Active Delay

(Note 11)

CL = 100pF

50

50

ns

(42) TCHDTH Direction Control Inactive Delay

(Note 11)

CL = 100pF

30

30

ns

(43) TCLGL GT Active Delay

(44) TCLGH GT Inactive Delay

(45) TRLRH RD Width

CL = 100pF

CL = 100pF

CL = 100pF

10

85

0

50

ns

10

85

0

50

ns

2TCLCL

2TCLCL

ns

- 75

- 50

(46) TOLOH Output Rise Time

From 0.8V to 2.0V

20

15

ns

(47) TOHOL Output Fall Time

From 2.0V to 0.8V

20

15

ns

NOTES:

11. Signal at 82C84A or 82C88 shown for reference only.

12. Setup requirement for asynchronous signal only to guarantee recognition at next CLK.

13. Applies only to t2 state (8ns into t3).

14. The 80C86 actively pulls the RQ/GT pin to a logic one on the following clock low time.

15. Status lines return to their inactive (logic one) state after CLK goes low and READY goes high.

24

FN2957.3

January 9, 2009