AM79C970A Просмотр технического описания (PDF) - Advanced Micro Devices

Номер в каталоге

Компоненты Описание

Список матч

AM79C970A

AM79C970A Datasheet PDF : 220 Pages

| |||

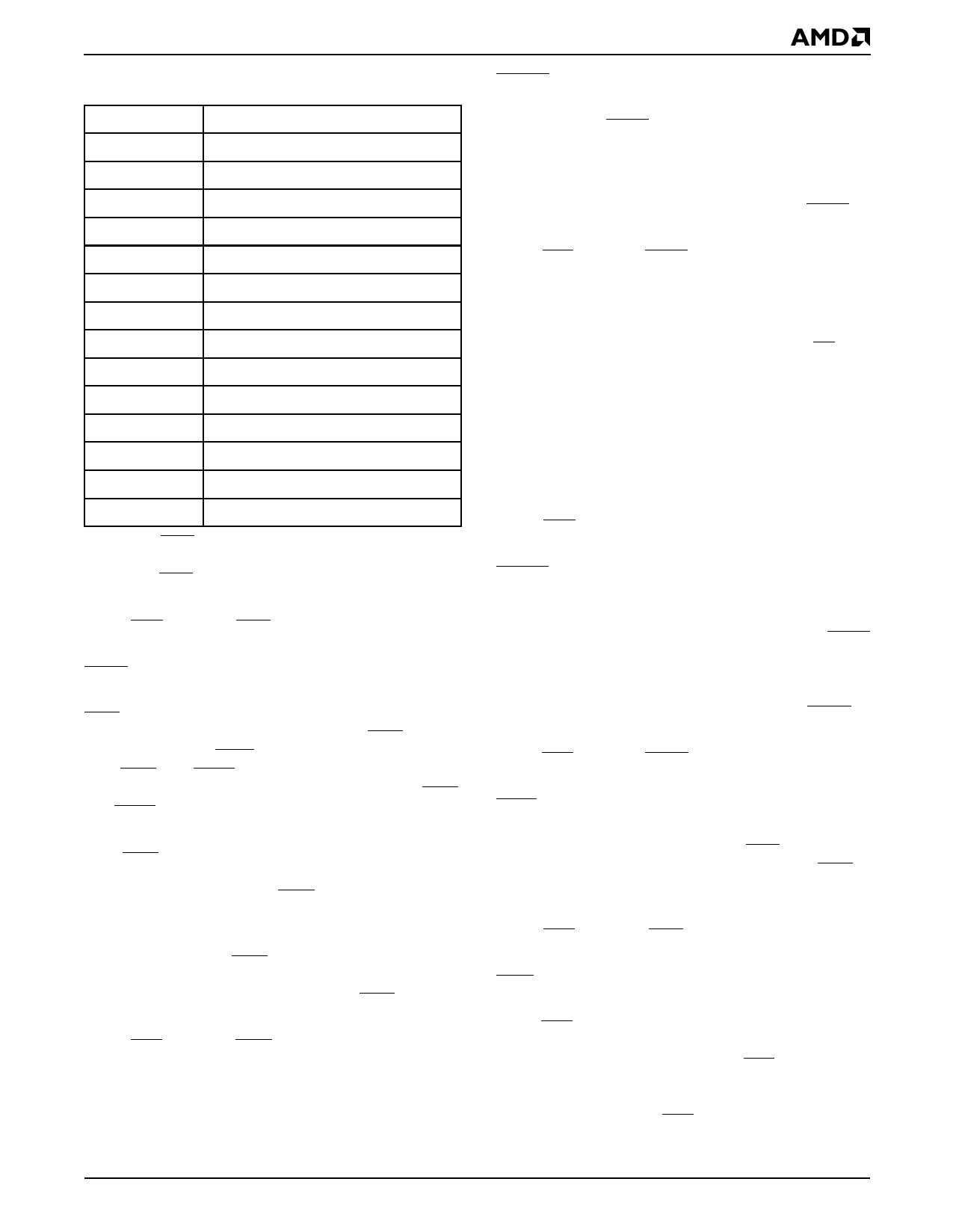

Table 1. Interrupt Flags

BABL

Babble

EXDINT

Excessive Deferral

IDON

Initialization Done

JAB

Jabber

MERR

Memory Error

MISS

Missed Frame

MFCO

Missed Frame Count Overflow

MPINT

Magic Packet Interrupt

RCVCCO

Receive Collision Count Overflow

RINT

Receive Interrupt

SLPINT

Sleep Interrupt

SINT

System Error

TINT

Transmit Interrupt

TXSTRT

Transmit Start

UINT

User Interrupt

By default INTA is an open-drain output. For applica-

tions that need a high-active edge sensitive interrupt

signal, the INTA pin can be configured for this mode by

setting INTLEVEL (BCR2, bit 7) to ONE.

When RST is active, INTA is an input for NAND tree

testing.

IRDY

Initiator Ready

Input/Output

IRDY indicates the ability of the initiator of the transac-

tion to complete the current data phase. IRDY is used

in conjunction with TRDY. Wait states are inserted until

both IRDY and TRDY are asserted simultaneously. A

data phase is completed on any clock when both IRDY

and TRDY are asserted.

When the PCnet-PCI II controller is a bus master, it as-

serts IRDY during all write data phases to indicate that

valid data is present on AD[31:0]. During all read data

phases the device asserts IRDY to indicate that it is

ready to accept the data.

When the PCnet-PCI II controller is the target of a

transaction, it checks IRDY during all write data phases

to determine if valid data is present on AD[31:0]. During

all read data phases the device checks IRDY to deter-

mine if the initiator is ready to accept the data.

When RST is active, IRDY is an input for NAND tree

testing.

LOCK

Lock

Input

In slave mode, LOCK is an input to the PCnet-PCI II

controller. A bus master can lock the device to guaran-

tee an atomic operation that requires multiple transac-

tions.

The PCnet-PCI II controller will never assert LOCK as

a master.

When RST is active, LOCK is an input for NAND tree

testing.

PAR

Parity

Input/Output

Parity is even parity across AD[31:0] and C/BE[3:0].

When the PCnet-PCI II controller is a bus master, it

generates parity during the address and write data

phases. It checks parity during read data phases.

When the PCnet-PCI II controller operates in slave

mode, it checks parity during every address phase.

When it is the target of a cycle, it checks parity during

write data phases and it generates parity during read

data phases.

When RST is active, PAR is an input for NAND tree

testing.

PERR

Parity Error

Input/Output

During any slave write transaction and any master read

transaction, the PCnet-PCI II controller asserts PERR

when it detects a data parity error and reporting of the

error is enabled by setting PERREN (PCI Command

register, bit 6) to ONE. During any master write trans-

action the PCnet-PCI II controller monitors PERR to

see if the target reports a data parity error.

When RST is active, PERR is an input for NAND tree

testing.

REQ

Bus Request

Input/Output

The PCnet-PCI II controller asserts REQ pin as a sig-

nal that it wishes to become a bus master. REQ is

driven high when the PCnet-PCI II controller does not

request the bus.

When RST is active, REQ is an input for NAND tree

testing.

RST

Reset

Input

When RST is asserted low, then the PCnet-PCI II con-

troller performs an internal system reset of the type

H_RESET (HARDWARE_RESET). RST must be held

for a minimum of 30 clock periods. While in the

H_RESET state, the PCnet-PCI II controller will disable

or deassert all outputs. RST may be asynchronous to

CLK when asserted or deasserted. It is recommended

Am79C970A

19