ACT-F128K32 Просмотр технического описания (PDF) - Aeroflex Corporation

Номер в каталоге

Компоненты Описание

Список матч

ACT-F128K32 Datasheet PDF : 20 Pages

| |||

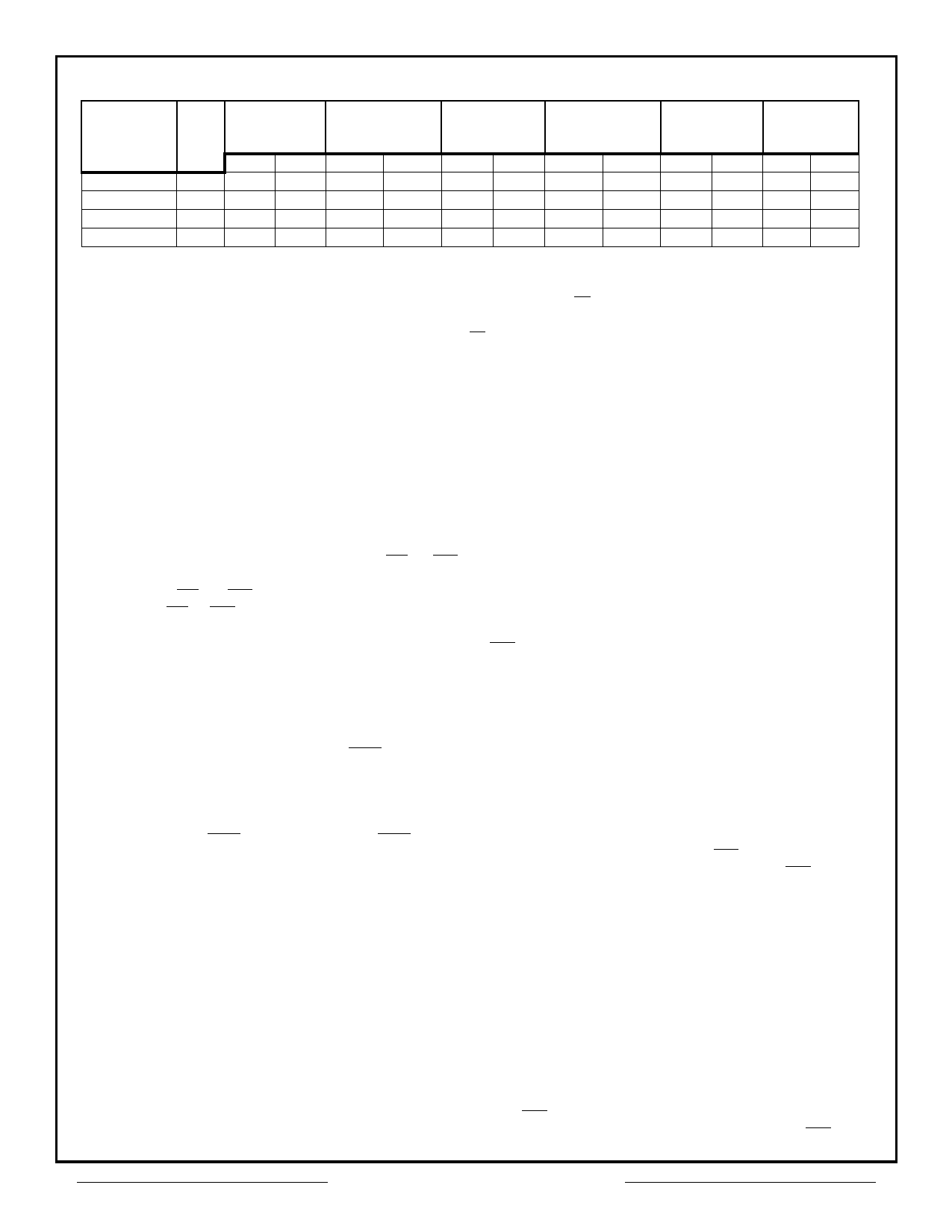

Table 3 — Commands Definitions

Command

Sequence

Bus

Write First Bus Write Second Bus Write Third Bus Write

Cycle

Cycle

Cycle

Cycle

Fourth Bus

Read/Write

Cycle

Req’d Addr Data Addr Data Addr Data Addr Data

Read/Reset

4 5555H AAH 2AAAH 55H 5555H F0H

RA

RD

Byte Program

6 5555H AAH 2AAAH 55H 5555H A0H

PA

PD

Chip Erase

6 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH

Sector Erase

6 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH

NOTES:

1. Address bit A15 = X = Don't Care. Write Sequences may be initiated with A15 in either state.

2. Address bit A16 = X = Don't Care for all address commands except for Program Address (PA) and Sector Address (SA).

3. RA = Address of the memory location to be read

PA = Address of the memory location to be programmed. Addresses are latched on the falling edge of the WE pulse.

SA = Address of the sector to be erased. The combination of A16, A15, A14 will uniquely select any sector.

4. RD = Data read from location RA during read Operation.

PD = Data to be programmed at location PA. Data is latched on the rising edge of WE.

Fifth Bus Write Sixth Bus Write

Cycle

Cycle

Addr Data Addr Data

2AAAH 55H 5555H 10H

2AAAH 55H SA 30H

default value ensures that no spurious alteration of the

memory content occurs during the power transition.

Refer to the AC Read Characteristics and Figure 7 for the

specific timing parameters.

BYTE PROGRAMING

The device is programmed on a byte-byte basis.

Programming is a four bus cycle operation. There are

two "unlock" write cycles. These are followed by the

program set-up command and data write cycles.

Addresses are latched on the falling edge of CE or WE,

whichever occurs later, while the data is latched on the

rising edge of CE or WE whichever occurs first. The

rising edge of CE or WE (whichever happens first) begins

programming using the Embedded Program Algorithm.

Upon executing the program algorithm command

sequence the system is not required to provide further

controls or timings. The device will automatically provide

adequate internally generated program pulses and verify

the programmed cell.

The automatic programming operation is completed

when the data on D7 (also used as Data Polling) is

equivalent to data written to this bit at which time the

device returns to the read mode and addresses are no

longer latched. Therefore, the device requires that a valid

address be supplied by the system at this particular

instance of time for Data Polling operations. Data Polling

must be performed at the memory location which is being

programmed.

Any commands written to the chip during the Embedded

Program Algorithm will be ignored.

Programming is allowed in any sequence and across

sector boundaries. Beware that a data "0" cannot be

programmed back to a “1". Attempting to do so may

cause the device to exceed programming time limits (D5

= 1) or result in an apparent success, according to the

data polling algorithm, but a read from reset/read mode

will show that the data is still “0". Only erase operations

can convert “0"s to “1"s.

Figure 3 illustrates the programming algorithm using

typical command strings and bus operations.

CHIP ERASE

Chip erase is a six bus cycle operation. There are two

'unlock' write cycles. These are followed by writing the

“set-up” command. Two more “unlock” write cycles are

then followed by the chip erase command.

Chip erase does not require the user to program the

device prior to erase. Upon executing the Embedded

Erase Algorithm command sequence (Figure 4) the

device will automatically program and verify the entire

memory for an all zero data pattem prior to electrical

erase. The erase is performed concurrently on all sectors

at the same time . The system is not required to provide

any controls or timings during these operations. Note:

Post Erase data state is all "1"s.

The automatic erase begins on the rising edge of the last

WE pulse in the command sequence and terminates

when the data on D7 is "1" (see Write Operation Status

section - Table 3) at which time the device retums to read

mode. See Figures 4 and 9.

SECTOR ERASE

Sector erase is a six bus cycle operation. There are two

"unlock" write cycles. These are followed by writing the

"setup" command. Two more "unlock" write cycles are

then followed by the sector erase command. The sector

address (any address location within the desired sector)

is latched on the falling edge of WE, while the command

(30H) is latched on the rising edge of WE. After a

time-out of 80µs from the rising edge of the last sector

erase command, the sector erase operation will begin.

Multiple sectors may be erased concurrently by writing

the six bus cycle operations as described above. This

sequence is followed with writes of the sector erase

command to addresses in other sectors desired to be

concurrently erased. The time between writes must be

less than 80µs otherwise that command will not be

accepted and erasure will start. It is recommended that

processor interrupts be disabled during this time to

guarantee this condition. The interrupts can be

re-enabled after the last Sector Erase command is

written. A time-out of 80µs from the rising edge of the

last WE will initiate the execution of the Sector Erase

command(s). If another falling edge of the WE occurs

Aeroflex Circuit Technology

6

SCD1667 REV A 4/28/97 Plainview NY (516) 694-6700