PCD5002 Просмотр технического описания (PDF) - Philips Electronics

Номер в каталоге

Компоненты Описание

Список матч

PCD5002 Datasheet PDF : 48 Pages

| |||

Philips Semiconductors

Advanced POCSAG and APOC-1 Paging

Decoder

Product specification

PCD5002

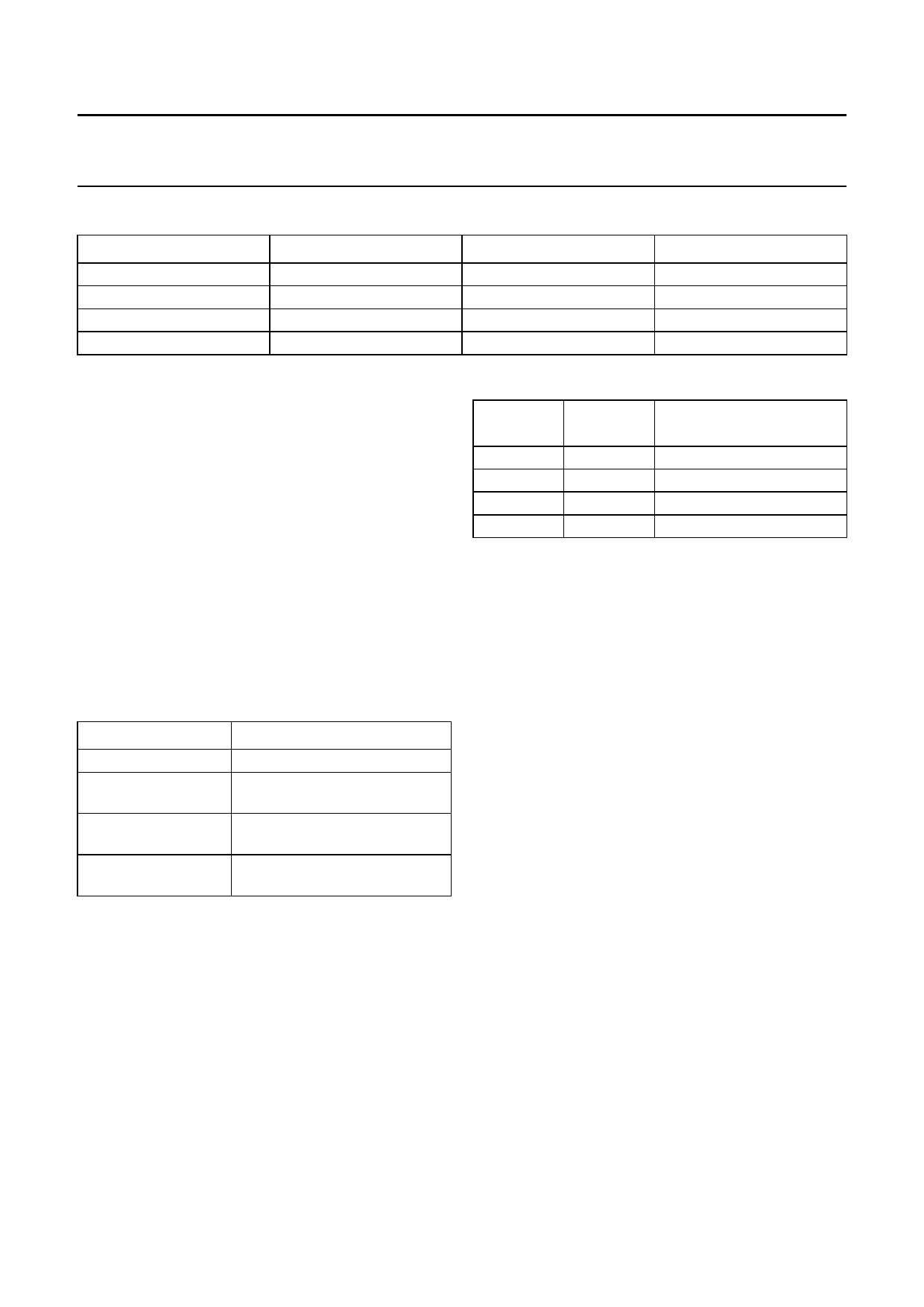

Table 1 POCSAG recommended call types and function bits

BIT 20 (MSB)

0

0

1

1

BIT 21 (LSB)

0

1

0

1

CALL TYPE

numeric

alert only 1

alert only 2

alphanumeric

DATA FORMAT

4-bits per digit

−

−

7-bits per ASCII character

The POCSAG standard only allows combinations of data

formats and function code bits as given in Table 1.

However, other (non-standard) combinations will be

decoded normally by the PCD5002.

8.4 Error correction

In the PCD5002 error correction methods have been

implemented as shown in Table 2.

Random error correction is default for both address and

message codewords. In addition, burst error correction

can be enabled by SPF programming. Up to 3 erroneous

bits in a 4-bit burst can be corrected.

The error type detected for each codeword is identified in

the message data output to the microcontroller, allowing

rejection of calls with too many errors.

Table 2 Error correction

ITEM

Preamble

Synchronization

codeword

Address codeword

Message codeword

CORRECTION

4 random errors in 31 bits

2 random errors in 32 bits

2 random errors, plus 4-bit burst

errors (optional)

2 random errors, plus 4-bit burst

errors (optional)

8.5 Operating states

The PCD5002 has 2 operating states:

• ON status

• OFF status.

The operating state is determined by a Direct Control input

(DON) and bit D4 in the control register (see Table 3).

Table 3 Truth table for decoder operating status

DON

INPUT

0

0

1

1

CONTROL

BIT D4

0

1

0

1

OPERATING STATUS

OFF

ON

ON

ON

8.6 ON status

In the ON status the decoder pulses the receiver and

oscillator enable outputs (RXE and ROE respectively)

according to the code structure and the synchronization

algorithm. Data received serially at the data input (RDI) is

processed for call reception.

The data protocol can be POCSAG or APOC-1.

Continuous data decoding upon reception of a special

sync word is also supported. The data protocol is selected

by SPF programming.

Reception of a valid paging call is signalled to the

microcontroller by an interrupt signal. The received

address and message data can then be read via the

I2C-bus interface.

8.7 OFF status

In the OFF status the decoder will neither activate the

receiver or oscillator enable outputs, nor process any data

at the data input. The crystal oscillator remains active to

permit communication with the microcontroller.

In both operating states an accurate timing reference is

available via the REF output. Using SPF programming the

signal periodicity may be selected as 32.768 kHz, 50 Hz,

2 Hz or 1⁄60 Hz.

8.8 Reset

The decoder can be reset by applying a positive pulse on

input pin RST. For successful reset at power-on, a HIGH

level must be present on the RST pin while the device is

powering-up.

1997 Jun 24

8