PCD5002 Просмотр технического описания (PDF) - Philips Electronics

Номер в каталоге

Компоненты Описание

Список матч

PCD5002 Datasheet PDF : 48 Pages

| |||

Philips Semiconductors

Advanced POCSAG and APOC-1 Paging

Decoder

Product specification

PCD5002

handbook, full pagewidth

OFF to ON status

preamble

switch on

sync word

no preamble

or sync word

(3 batches)

carrier detect

preamble

sync word

TX off

time out

preamble receive 1 preamble

no preamble (1 batch)

long fade recovery

sync word

preamble

batch zero detect

batch zero ID

sync word

no sync word

batch zero identify

no batch zero ID

batch

zero ID

cycle receive

sync

no sync

word

word

preamble

short fade recovery

no sync word

or preamble

sync word

transmitter off

no preamble

TX off time out

(1 batch)

preamble

sync word

preamble receive 2

MGD269

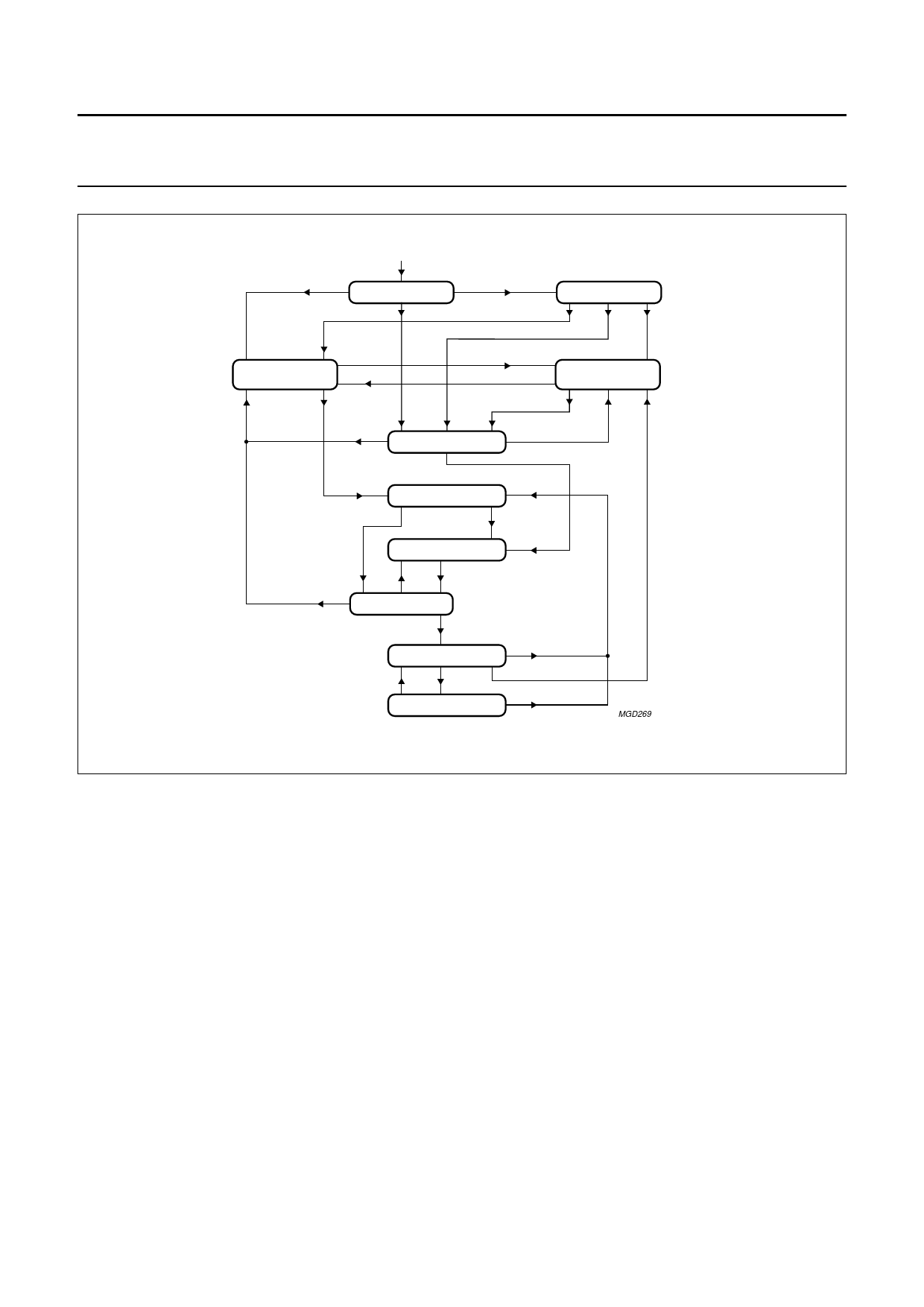

Fig.5 APOC-1 synchronization algorithm.

8.14 APOC-1 synchronization strategy

The synchronization strategy in APOC-1 is an extended

version of the ACCESS® scheme and is illustrated in Fig.5.

The PCD5002 counts the number of batches in a

transmission, starting from the first batch received after

preamble. Counter overflow occurs due to the size of a

cycle, as determined by SPF programming.

Initially, after switching to the ON status, the decoder will

be in the switch-on mode. Here the receiver will be

enabled for up to 3 batches, testing for preamble and sync

word. Detection of preamble causes the device to switch

to the ‘preamble receive’ mode, while any enabled sync

word enters the ‘batch zero detect’ mode. Failure to detect

either will cause the device to switch to the ‘carrier detect’

mode.

In the preamble receive 1 mode the PCD5002 searches

for a sync word, the receiver remaining enabled while

preamble is detected. As soon as an enabled sync word is

found the ‘batch zero identify’ mode is started.

If preamble is not found within one batch duration then the

‘long fade recovery’ mode is entered.

When in batch zero detect mode the PCD5002 switches

on every batch to maintain synchronization and check for

the batch zero identifier. Detection of the batch zero

identifier activates the ‘cycle receive’ mode. When

synchronization is lost the ‘long fade recovery’ mode is

entered. ‘preamble receive’ mode is entered when

preamble is detected.

In the batch zero identify mode the first codeword

immediately after the sync word of the first batch is

compared with the programmed batch zero identifier.

Failure to detect the batch zero identifier will cause the

device to enter the ‘short fade recovery’ mode.

When this comparison is successful the function bits

determine whether any broadcast message will follow.

Any function bit combination other than ‘1,1’ will cause the

PCD5002 to accept message codewords until terminated

by a valid address codeword.

1997 Jun 24

11