IDT72103 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72103 Datasheet PDF : 30 Pages

| |||

IDT72103, IDT72104

CMOS PARALLEL-SERIAL FIFO 2,048 x 9, 4,096 x 9

INDUSTRIAL TEMPERATURE RANGE

DESCRIPTION (Continued)

A serial input, a serial output and two 9-bit parallel ports

make four modes of data transfer possible: serial-to-parallel,

parallel-to-serial, serial-to-serial, and parallel-to-parallel. These

devices are expandable in both depth and width for all of these

operational configurations.

These FIFOs may be configured to handle serial word

widths of four or greater using IDT’s unique Flexishift feature.

Flexishift allows serial width and depth expansion without

external components. For example, you may configure a 4K

x 24 FIFO using three IDT72104s in a serial width expansion

configuration.

Seven flags are provided to signal memory status of the

FIFO. The flags are FF (Full), AF (7/8 full), FF–1 (Full-minus-

one), EF (Empty), AE (1/8 full), EF+1 (Empty-plus-one), and

HF (Half-full).

Read (R) and Write (W) control pins are provided for

asynchronous and simultaneous operations. An Output En-

able (OE) control pin is available on the parallel output port for

high-impedance control. The depth expansion control pins XO

and Xl are provided to allow cascading for deeper FlFOs.

The IDT72103/72104 are manufactured using IDT’s CMOS

technology.

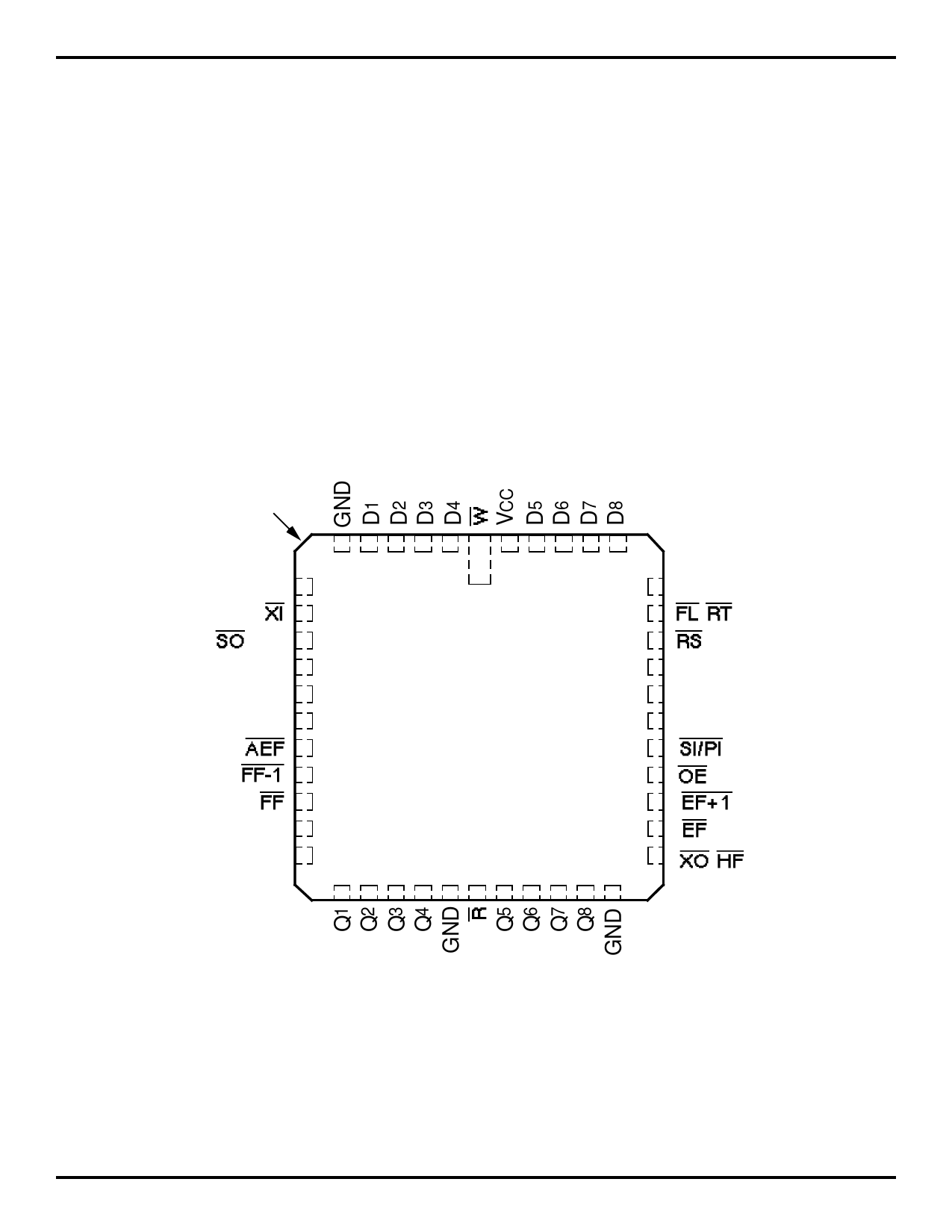

PIN CONFIGURATIONS

INDEX

D0

/PO

SOX

SOCP

SO

Q0

GND

6 5 4 3 2 44 43 42 41 40

7

1

39

8

38

9

37

10

36

11

35

12

34

13

33

14

32

15

31

16

30

17

29

18 19 20 21 22 23 24 25 26 27 28

GND

/

SI

SICP

SIX

/

2753 drw 03

PLCC (J44-1, order code: J)

TOP VIEW

2