CS61881-IB Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS61881-IB Datasheet PDF : 28 Pages

| |||

CS61881

Octal E1 Analog Front End

Features

s Octal E1 Line Interface Unit Compliant with G.703

s Very Low Power <100mW per Channel

s Single Supply 3.3 V Operation, 5 V Tolerant I/O

s No External Component Changes for 120 Ω/75 Ω

Operation

s Analog LOS Detection per ITU G.775

s Transmitter Short Circuit Current Limiter (<50mA)

s TX Drivers with Fast Tristate and Power Down

s Transmit Return Loss Exceeds ETS 300 166

s JTAG Boundary Scan compliant to IEEE 1149.1

s 144 Pin LQFP or 160 BGA Package

ORDERING INFORMATION

CS61881-IQ

CS61881-IB

144-pin LQFP

160-pin BGA

Description

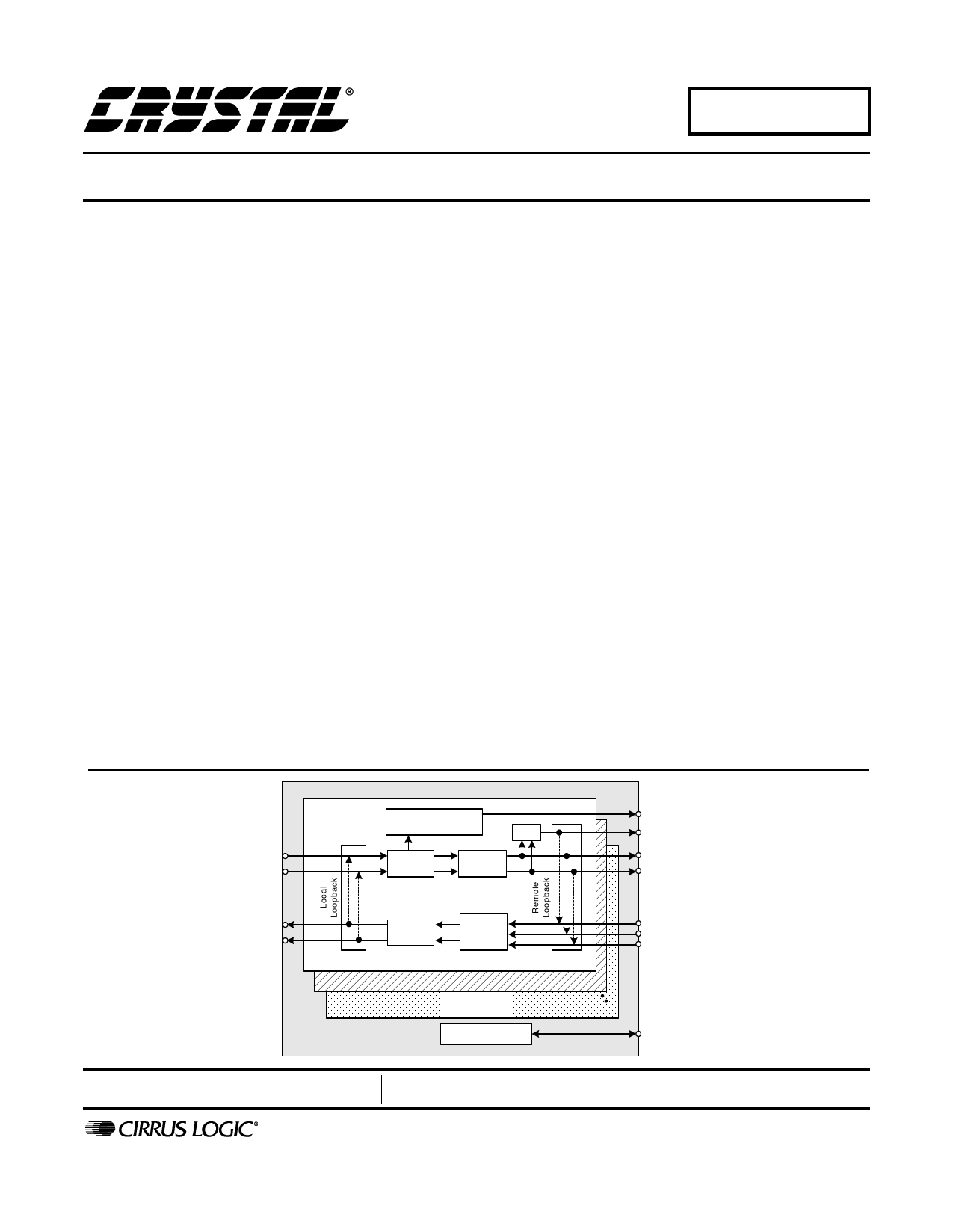

The CS61881contains eight analog front ends that each

provide the line interface for E1 transmission systems.

The device contains eight receivers and transmitters

supporting a 2.048 Mbps data rate compliant to ITU

G.703. This device is commonly used with external cir-

cuitry that supplies data encoding/decoding, clock

recovery, and jitter attenuation.

The CS61881 makes use of ultra low power matched im-

pedance transmitters to reduce power beyond that

achieved by traditional driver designs. By achieving a

more precise line match, this technique also provides su-

perior return loss characteristics, exceeding ETS 300

166. The internal line matching circuitry reduces the ex-

ternal component count and eliminates the need to

change components to support both 75 Ω and 120 Ω

lines. All transmitters have controls for independent pow-

er down and tristate.

The receiver has a high noise margin, providing reliable

data recovery even with cable attenuation of over 12 dB.

It has an impedance matched front end, eliminating the

need to change components to support both 75 Ω and

120 Ω line impedances. The receiver also incorporates

LOS detection compliant to the most recent

specifications.

A five wire JTAG interface is also provided for improved

diagnostics and reduced manufacturing cost.

RTIP

RRING

G.775

LOS

Peak

Detect

XOR

Slicer

LOS

RCLK

RPOS

RNEG

TTIP

TRING

Driver

Pulse

Shaper

JTAG Interface

1

2

8

TCLK

TPOS

TNEG

JTAG

Serial

Port

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2000

(All Rights Reserved)

APR ‘00

DS451PP3

1