70P2352-IGT Просмотр технического описания (PDF) - Teridian Semiconductor Corporation

Номер в каталоге

Компоненты Описание

Список матч

70P2352-IGT Datasheet PDF : 42 Pages

| |||

78P2352

Dual Channel

OC-3/ STM1-E/ E4 LIU

REGISTER DESCRIPTION (CONTINUED)

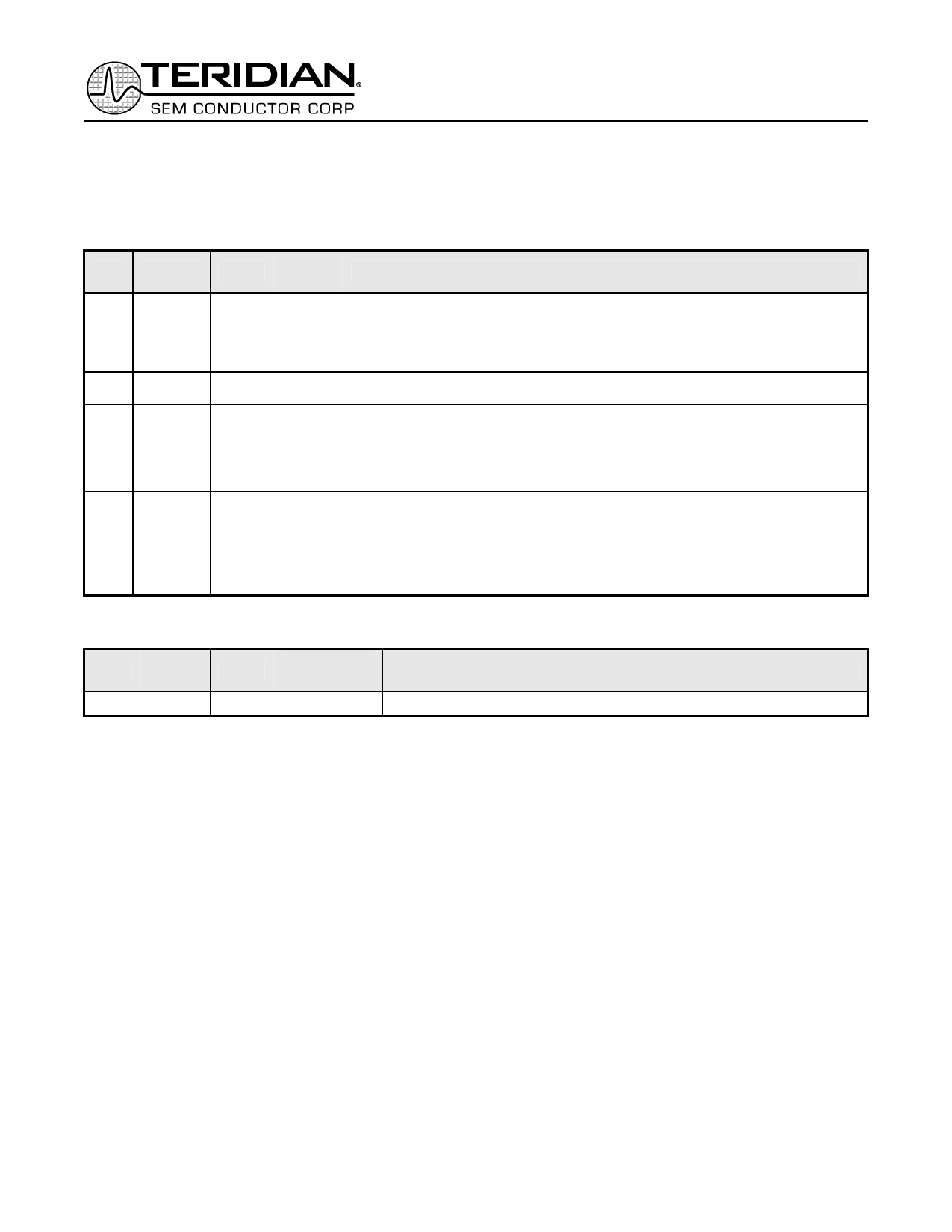

ADDRESS 0-1: INTERRUPT CONTROL REGISTER

This register selects the events that would cause the interrupt pins to be activated. User may set as many bits as

required.

BIT

NAME

TYPE

DFLT

VALUE

DESCRIPTION

Interrupt Pin Polarity Selection:

7 INPOL R/W

0

0 : Interrupt output is active-low (default)

1 : Interrupt output is active-high

6:2

--

1 MTLOL

0 MFERR

R/W

R/W

R/W

01000

1

1

Reserved for future use

TXLOL Error Mask (active low):

Gates the TXLOL register bit to the INTTXxB interrupt pin.

0: Mask

1: Pass

FIERR Error Mask (active low):

Gates the respective FIERR register bit to the INTTXxB interrupt pin.

0: Mask

1: Pass

ADDRESS 0-2: RESERVED

BIT NAME TYPE

DFLT

VALUE

7:0

--

R/W XXXXXXX0

DESCRIPTION

Reserved.

Page: 11 of 42

2006 Teridian Semiconductor Corporation

Rev. 2.4