AD9684 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

Список матч

AD9684 Datasheet PDF : 64 Pages

| |||

AD9684

Product

Overview

Online

Documentation

Design

Resources

Discussion

Sample

& Buy

Data Sheet

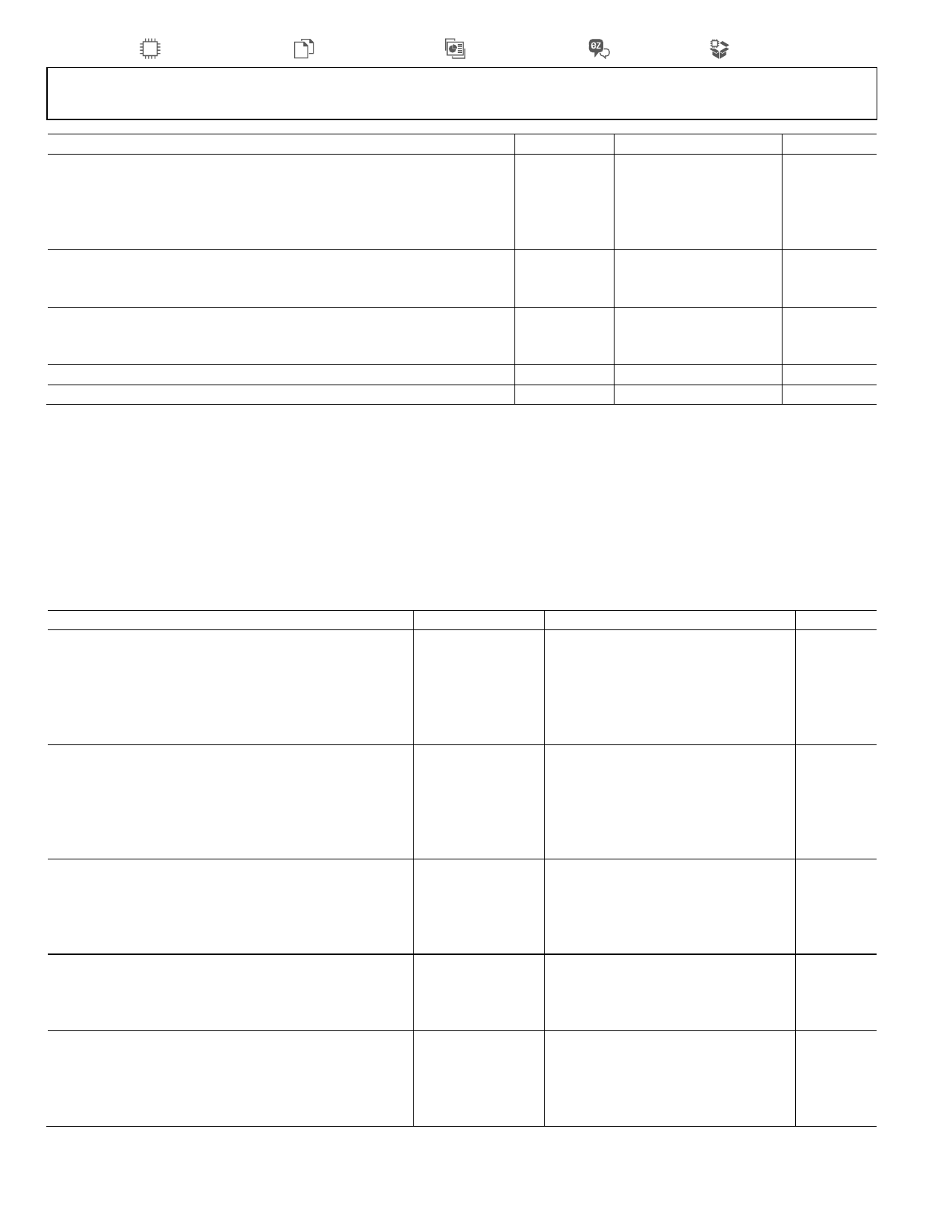

Parameter1

WORST OTHER, EXCLUDING SECOND OR THIRD HARMONIC3

fIN = 10 MHz

fIN = 170 MHz

fIN = 340 MHz

fIN = 450 MHz

fIN = 765 MHz

fIN = 985 MHz

fIN = 1950 MHz

TWO-TONE INTERMODULATION DISTORTION (IMD), AIN1 AND AIN2 = −7 dBFS

fIN1 = 185 MHz, fIN2 = 188 MHz

fIN1 = 338 MHz, fIN2 = 341 MHz

CROSSTALK4

FULL POWER BANDWIDTH

Temperature Min Typ Max Unit

25°C

−93

dBFS

Full

−92 −76 dBFS

25°C

−90

dBFS

25°C

−92

dBFS

25°C

−89

dBFS

25°C

−89

dBFS

25°C

−85

dBFS

25°C

−88

dBFS

25°C

−87

dBFS

25°C

96

dB

25°C

2

GHz

1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for definitions and for details on how these tests were completed.

2 Noise density is measured at a low analog input frequency (30 MHz).

3 See Table 9 for the recommended settings for full-scale voltage and buffer current control.

4 Crosstalk is measured at 170 MHz with a −1.0 dBFS analog input on one channel and no input on the adjacent channel.

DIGITAL SPECIFICATIONS

AVDD1 = 1.25 V, AVDD2 = 2.5 V, AVDD3 = 3.3 V, DVDD = 1.25 V, DRVDD = 1.25 V, SPIVDD = 1.8 V, specified maximum sampling

rate (500 MSPS), 1.7 V p-p full-scale differential input, 1.0 V internal reference, AIN = −1.0 dBFS, default SPI settings, TA = 25°C, unless

otherwise noted.

Table 3.

Parameter

CLOCK INPUTS (CLK+, CLK−)

Logic Compliance

Differential Input Voltage

Input Common-Mode Voltage

Input Resistance (Differential)

Input Capacitance

SYNC INPUTS (SYNC+, SYNC−)

Logic Compliance

Differential Input Voltage

Input Common-Mode Voltage

Input Resistance (Differential)

Input Capacitance (Differential)

LOGIC INPUTS (SDIO, SCLK, CSB, PDWN/STBY)

Logic Compliance

Logic 1 Voltage

Logic 0 Voltage

Input Resistance

LOGIC OUTPUT (SDIO)

Logic Compliance

Logic 1 Voltage (IOH = 800 µA)

Logic 0 Voltage (IOL = 50 µA)

LOGIC OUTPUTS (FD_A, FD_B)

Logic Compliance

Logic 1 Voltage

Logic 0 Voltage

Input Resistance

Temperature

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Min

Typ

Max

Unit

LVDS/LVPECL

600

1200

1800 mV p-p

0.85

V

35

kΩ

2.5

pF

LVDS/LVPECL

400

1200

1800 mV p-p

0.6

0.85

2.0

V

35

kΩ

2.5

pF

CMOS

0.8 × SPIVDD

V

0

0.2 × SPIVDD

V

30

kΩ

CMOS

0.8 × SPIVDD

V

0.2 × SPIVDD

V

CMOS

0.8

SPIVDD

V

0

0

V

30

kΩ

Rev. 0 | Page 6 of 64