HPMX-5002-STR Просмотр технического описания (PDF) - HP => Agilent Technologies

Номер в каталоге

Компоненты Описание

Список матч

HPMX-5002-STR Datasheet PDF : 14 Pages

| |||

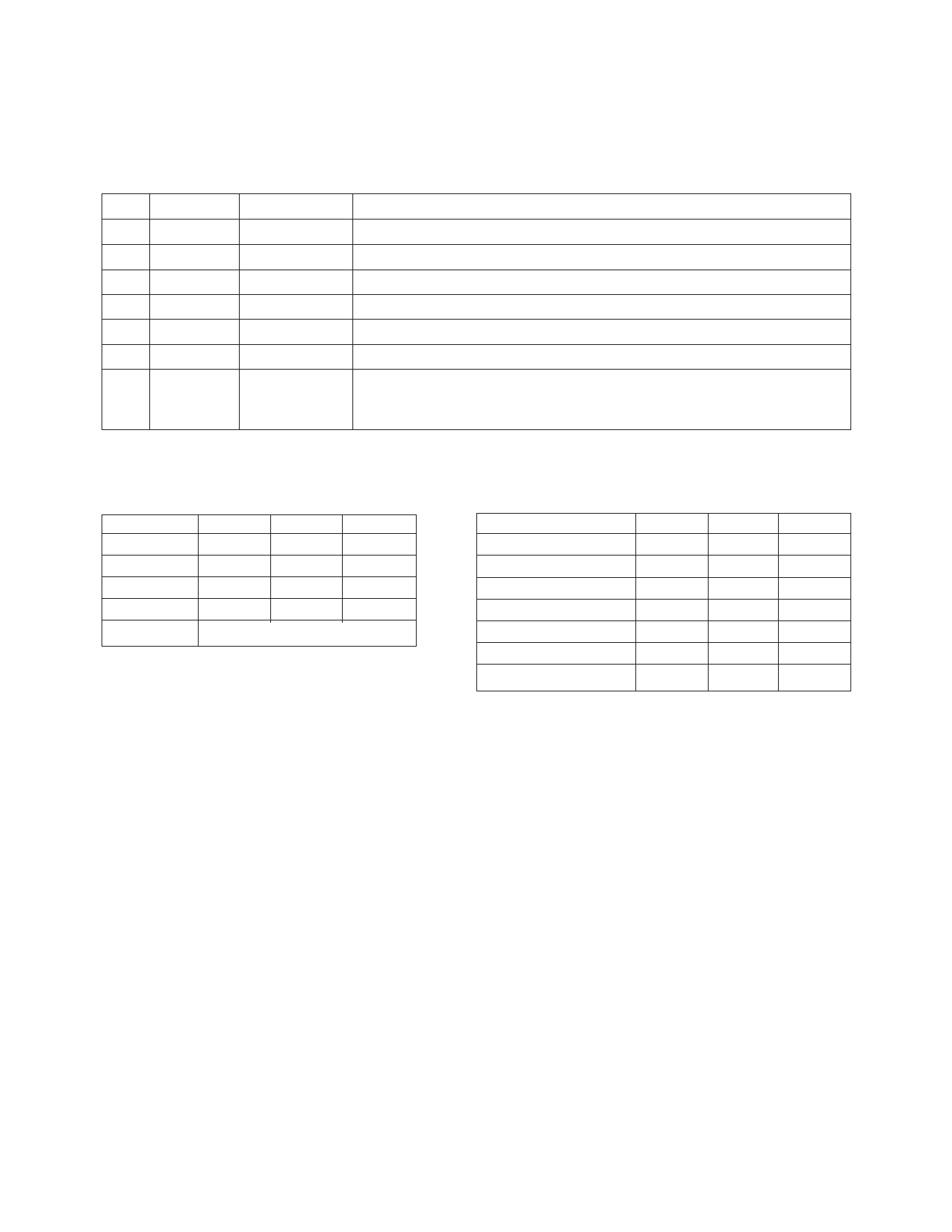

HPMX-5002 Pin Description, continued

No. Mnemonic I/O Type

Description

41 DC1B

Analog DC External capacitor connection for decoupling IF limiting amplifier

42 VSUB

Ground

Substrate connection

43

XLO

CMOS I/P Controls bias to VCO and PLL components in conjunction with PLL pin

44

PLL

CMOS I/P Controls bias to VCO and PLL components in conjunction with XLO pin

45

RX

CMOS I/P Controls bias to receive signal path, RSSI, data slicer

47

BGR

Analog DC External capacitor connection for decoupling bandgap reference voltage

18,19, N/C

36, 46,

48

Not

connected

All unconnected pins should be connected to a low-noise ground

Table 1: HPMX-5002 Mode Control

(CMOS Logic Levels)

Mode

PLL

TX

RX

STBY

“flywheel”

PLL

XLO

RX

1

0

1

0

0

1

1

0

0

1

1

1

see text

Table 2: HPMX-5002 PLL Divider Programming

(CMOS Logic Levels)

REF divide by:

9

12

16

Not defined

LO2 divide by:

90

216

DIV1

1

0

0

1

DIV2

0

0

1

1

X

X

X

X

DIV3

X

X

X

X

0

1

7-110