KL5KUSB201 Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

Список матч

KL5KUSB201 Datasheet PDF : 21 Pages

| |||

Kawasaki USB device

KL5KUSB201

Datasheet (digest) rev 1.1E page 11/21

6. Signal Description

Table 6 describes signal function description and related name in UTMI.

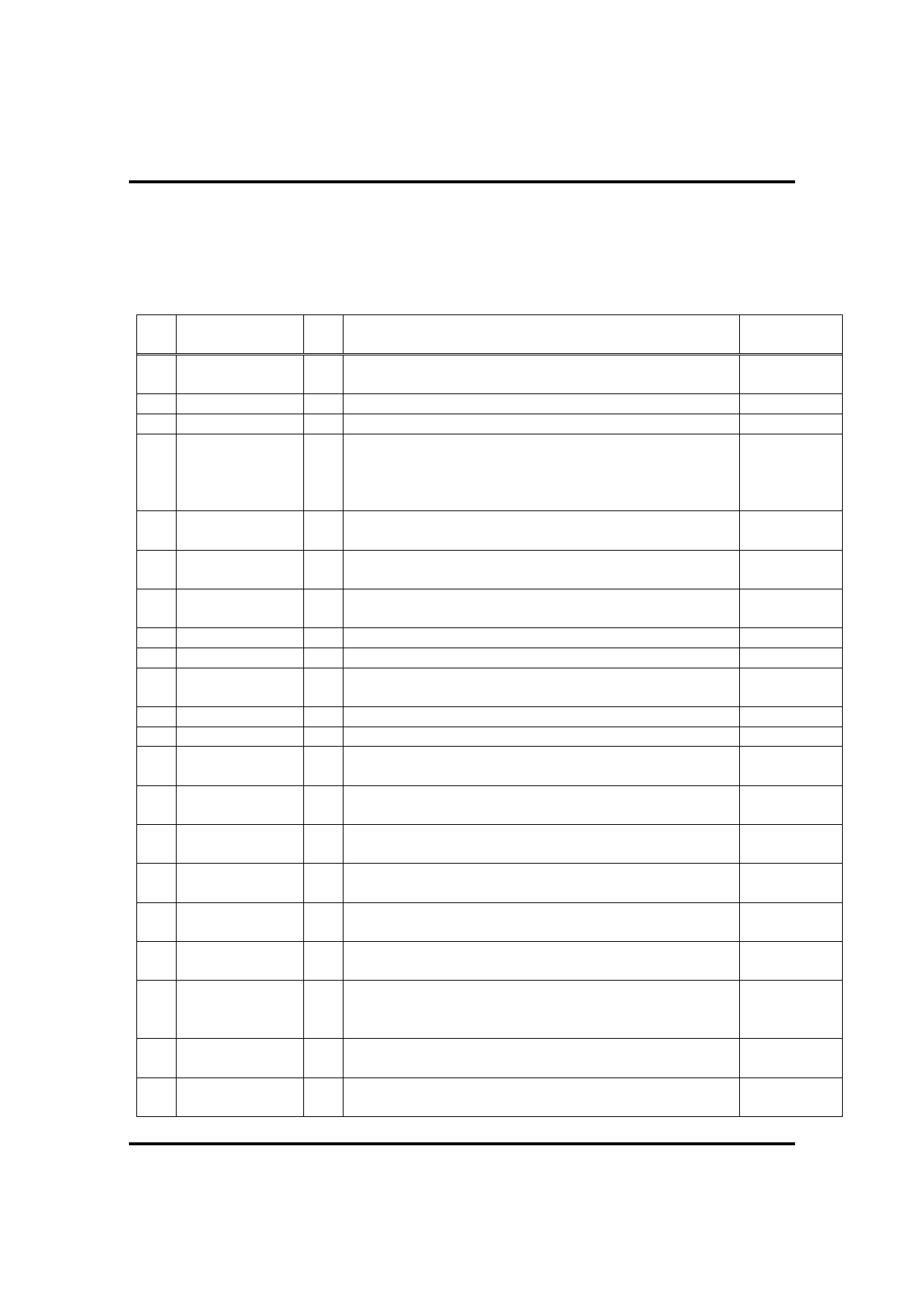

Table 6 Signal Description

No Signal Name I/O

Description

UTMI

name

1 REXT

O Reference bias current pin. Connect to GND via

--

external resistor Rext.

2 HSDP

I/O High Speed DP pin. Connect to USB Bus D+.

DP

3 HSDM

I/O High Speed DM pin. Connect to USB Bus D-.

DM

4 RPU_ENA

O Pull up resister source pin. Connect to external

--

resistor Rpu, which is tied to USB bus D+.

RPU_ENA becomes 3-state in High Speed

operation.

5 FSDP

I/O Full Speed DP pin. Connect to USB Bus D+ via (DP)

termination resistor Rs.

6 FSDM

I/O Full Speed DM pin. Connect to USB Bus D- via (DM)

termination resistor Rs.

7 XIN

I 48MHz clock input pin. Connect to crystal oscillator

--

or crystal oscillation circuit.

8 XOUT

O 48MHz clock output pin for crystal oscillation circuit.

--

9 FS_HSN

I USB bus speed control pin.

XcvrSelect

10 PU_SE0N

I Termination control pin. With FS_HSN and MODE, TermSelect

LSI operation mode is selected.

11 CKOUT

O SIE bus clock pin. Frequency is 30MHz.

CLK

12 RXACT

O USB packet received signal.

RXActive

13 RXVLD

O SIE bus out data valid signal. Active H.

RXValid

(RXValidH)

14 CRCERR

O CRC error detection signal. Active when CRC logic

--

is enabled.

15 RXERR

O Receive error detection signal. RX error indicator RXError

except for CRC error.

16 TXACT

I USB bus data transmit control signal. SIE bus TXValid

switches from output to input when active.

(TXValidH)

17 TXRDY

O SIE input data ready signal. Valid when TXACT is TXReady

active.

18 CRCACT

I CRC detection logic enable signal. Also used for

--

data transmit abortion.

19 SIE_DAT[15:0] I/O 16bit parallel 3-state SIE data bus. Synchronized Data15-8,

with CKOUT. Data direction is input when TXACT Data7-0

assertion. Default direction is output.

20 WDVLD

I/O SIE data width indication signal. If last SIE data is a ValidH

byte data, WDVLD is asserted.

21 RSTN

I Hardreset signal. Active L. Assertion required when RST

power on and USB reset recognition.

(assert H)

Copyright © 2002 Kawasaki Microelectronics Inc. Kawasaki LSI Inc. All rights reserved.