VT82C586B Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

Список матч

VT82C586B Datasheet PDF : 69 Pages

| |||

9,$7HFKQRORJLHV,QF

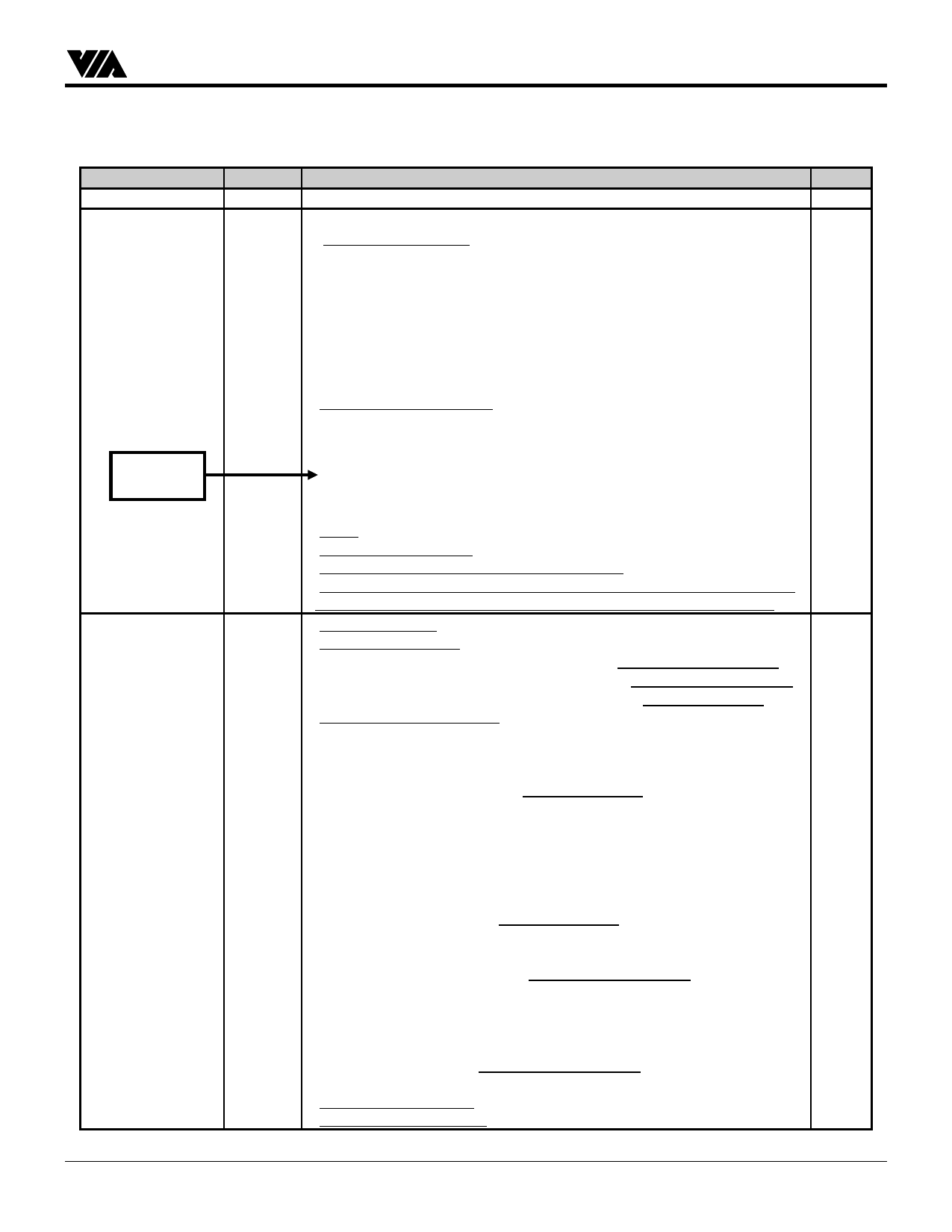

REVISION HISTORY

VT82C586B

Document Release

Revision 0.1

Revision 0.5

Incorrect

Change

Revision 1.0

Date

10/13/96

12/23/96

reprinted

1/8/97

to fix

Acrobat

PDF file

size

problem

5/13/97

Revision

Initial release for 586A

Update to reflect 586B:

• Updated pin definitions:

Pins 18,31,33,58,60,131,133 (removed EXTSMI2-7 & DACEN)

Pins 77-78,80-83,85-86 (added GPI8-15 and GPO8-15)

Pins 94,87-88,92,136 (changed to GPIO0-4 and added alternate functions)

Pins 90,106,137 (added MIRQ0, MIRQ1, and MIRQ2 functions)

Pins 91,93,103,107 (changed to PWRBTN#, RI#, VDD-5VSB, PWRON)

Pins 113-114,116-119,121-122 (added GPI, GPO, and EXTSMI functions)

Fixed doc error DACK0-7 pin names changed to active low (DACK0-7#)

Removed options: IRQ12 (pin 137), strap (pin 48), RTCAS (pin 94)

• Updated register definitions

Removed VIA-specific port A8/A9 registers

Updated function 0 Rx5-4[3], Rx7-6[13], Rx41[0-4,6-7], Rx42[4-7], Rx44,

Rx46[2-4], Rx47[3], Rx48[3], Rx4A[4-6], Removed Rx50 (MDRQ)

Rx55[7-4] change PIRQD# to MIRQ1, Rx56 swap A/B, Rx57 swap C/D

Added 58-5B for PnP, XD, KBC/RTC config; added 60-6F for DDMA ctrl

Removed power mgmt regs 80-94 & added function 3 ACPI Power Mgmt

• Straps: moved 95-96 to 5A, allow RW after powerup, removed strap XD3

• Expanded CMOS RAM: added ports 72-75 & table 5 CMOS Reg Summary

• Added Power Management Subsystem Overview

• Incorporated App Note #53 APM-Compliant Pwr Mgmt Model of 82C586A

• Added AC Timing Section with IDE Interface Timing Diagrams & Specs

• Overview Changes: Added System Block Diagram

• Pin Function Changes:

Pin 90 added alternate function "POS" output (3040F and 3041 silicon)

Pin 106 added alternate function "IRQ8#" input (3040F and 3041 silicon)

Pin 137 added alternate function "SDDIR" output (3041 only silicon)

• Register Definition Changes:

Fixed typos: Port 75 note, Fn0 Rx48[3], Rx55-57[7:0]; Fn1 Rx4[7]; Fn2

Rx3C-3D; Fn3 Rx26[9], Rx2F, Rx62-63, Table 7

Added missing register: Function 0 Rx59[3] MIRQ Pin Config Register

Function 0 PCI-to-ISA Bridge (3041 only silicon)

Rx08[7:0] (changed) Revision Code Register

Rx2C[31:0] (new) Subsystem ID Register (read)

Rx41[0] (changed) ISA Test Mode Register

Rx46[7:5] and Rx48[5:4] (new) Misc Control Registers 1 and 3

Rx5C[0] (new) DMA Control Register

Rx70[31:0] (new) Subsystem ID Register (write)

Function 1 IDE Controller (3041 only silicon)

Rx43[7] (new) FIFO Configuration Register

Rx44[1:0] (new) Misc Control Register 1

Function 3 Power Management (3040F and 3041 silicon)

Rx04[0] (moved to Rx41[7]) Command Register

Rx08[7:0] (changed) Revision ID Register

Rx10[4:1], Rx14 (changed) Processor Control and Processor Level 2

Rx20[31:0] (moved to Rx48) I/O Base Address Register

Power Management I/O(3040F and 3041 silicon)

Rx40[6:5] (new) GPIO Direction Control Register

• Electrical Spec Changes: Added PCI Cycle Timing

• Mechanical Spec Changes: Added marking specs for 3040E/F, 3041 silicon

Initials

DH

DH

DH

Revision 1.0 May 13, 1997

-i-

Revision History