IDT723632L Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT723632L Datasheet PDF : 26 Pages

| |||

IDT723622/723632/723642 CMOS SyncBiFIFO™

256 x 36 x 2, 512 x 36 x 2, 1024 x 36 x 2

COMMERCIAL TEMPERATURE RANGE

port-B operation.

The port-B control signals are identical to those of port A

with the exception that the port-B write/read select (W/RB) is

the inverse of the port-A write/read select (W/RA). The state

of the port-B data (B0-B35) outputs is controlled by the port-

B chip select (CSB) and port-B write/read select (W/RB). The

B0-B35 outputs are in the high-impedance state when either

CSB is HIGH or W/RB is LOW. The B0-B35 outputs are active

when CSB is LOW and W/RB is HIGH.

Data is loaded into FIFO2 from the B0-B35 inputs on a

LOW-to-HIGH transition of CLKB when CSB is LOW, W/RB is

LOW, ENB is HIGH, MBB is LOW, and IRB is HIGH. Data is

read from FIFO1 to the B0-B35 outputs by a LOW-to-HIGH

transition of CLKB when CSB is LOW, W/RB is HIGH, ENB is

HIGH, MBB is LOW, and ORB is HIGH (see Table 3) . FIFO

reads and writes on port B are independent of any concurrent

port-A operation.

The setup and hold time constraints to the port clocks for

the port chip selects and write/read selects are only for

enabling write and read operations and are not related to high-

impedance control of the data outputs. If a port enable is LOW

during a clock cycle, the port’s chip select and write/read

select may change states during the setup and hold time

window of the cycle.

When a FIFO output-ready flag is LOW, the next data

word is sent to the FIFO output register automatically by the

LOW-to-HIGH transition of the port clock that sets the output-

ready flag HIGH. When the output-ready flag is HIGH, an

available data word is clocked to the FIFO output register only

when a FIFO read is selected by the port’s chip select, write/

read select, enable, and mailbox select.

SYNCHRONIZED FIFO FLAGS

Each FIFO is synchronized to its port clock through at

least two flip-flop stages. This is done to improve flag-signal

reliability by reducing the probability of metastable events

when CLKA and CLKB operate asynchronously to one an-

other. ORA, AEA, IRA, and AFA are synchronized to CLKA.

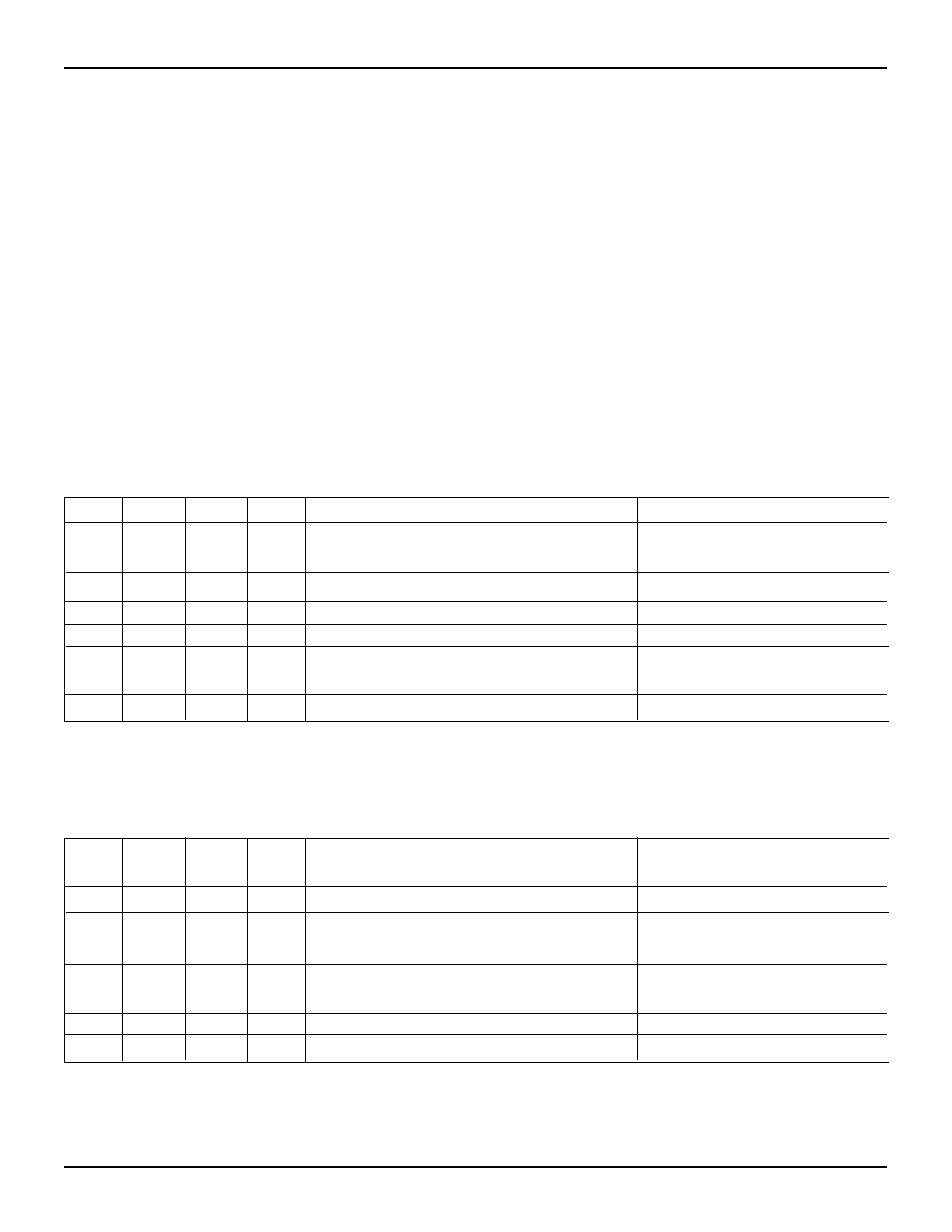

ORB, AEB, IRB, and AFB are synchronized to CLKB. Tables

4 and 5 show the relationship of each port flag to FIFO1 and

FIF02.

CSA

H

L

L

L

L

L

L

L

W/RA

X

H

H

H

L

L

L

L

ENA

X

L

H

H

L

H

L

H

MBA

X

X

L

H

L

L

H

H

CLKA

X

X

↑

↑

X

↑

X

↑

A0-A35 OUTPUTS

In high-impedance state

In high-impedance state

In high-impedance state

In high-impedance state

Active, FIFO2 output register

Active, FIFO2 output register

Active, mail2 register

Active, mail2 register

Table 2. Port-A Enable Functlon Table

PORT FUNCTION

None

None

FIFO1 write

Mail1 write

None

FIFO2 read

None

Mail2 read (set MBF2 HIGH)

CSB W/RB ENB MBB CLKB

H

X

X

X

X

L

L

L

X

X

L

L

H

L

↑

L

L

H

H

↑

L

H

L

L

X

L

H

H

L

↑

L

H

L

H

X

L

H

H

H

↑

B0-B35 OUTPUTS

In high-impedance state

In high-impedance state

In high-impedance state

In high-impedance state

Active, FIFO1 output register

Active, FIFO1 output register

Active, mail1 register

Active, mail1 register

Table 3. Port-B Enable Function Table

PORT FUNCTION

None

None

FIFO2 write

Mail2 write

None

FIFO1 read

None

Mail1 read (set MBF1 HIGH)

5.22

11