IDT72132 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72132 Datasheet PDF : 13 Pages

| |||

IDT72132, IDT72142

CMOS SERIAL-TO-PARALLEL FIFO 2048 x 9 AND 4096 x 9

COMMERCIAL TEMPERATURE RANGES

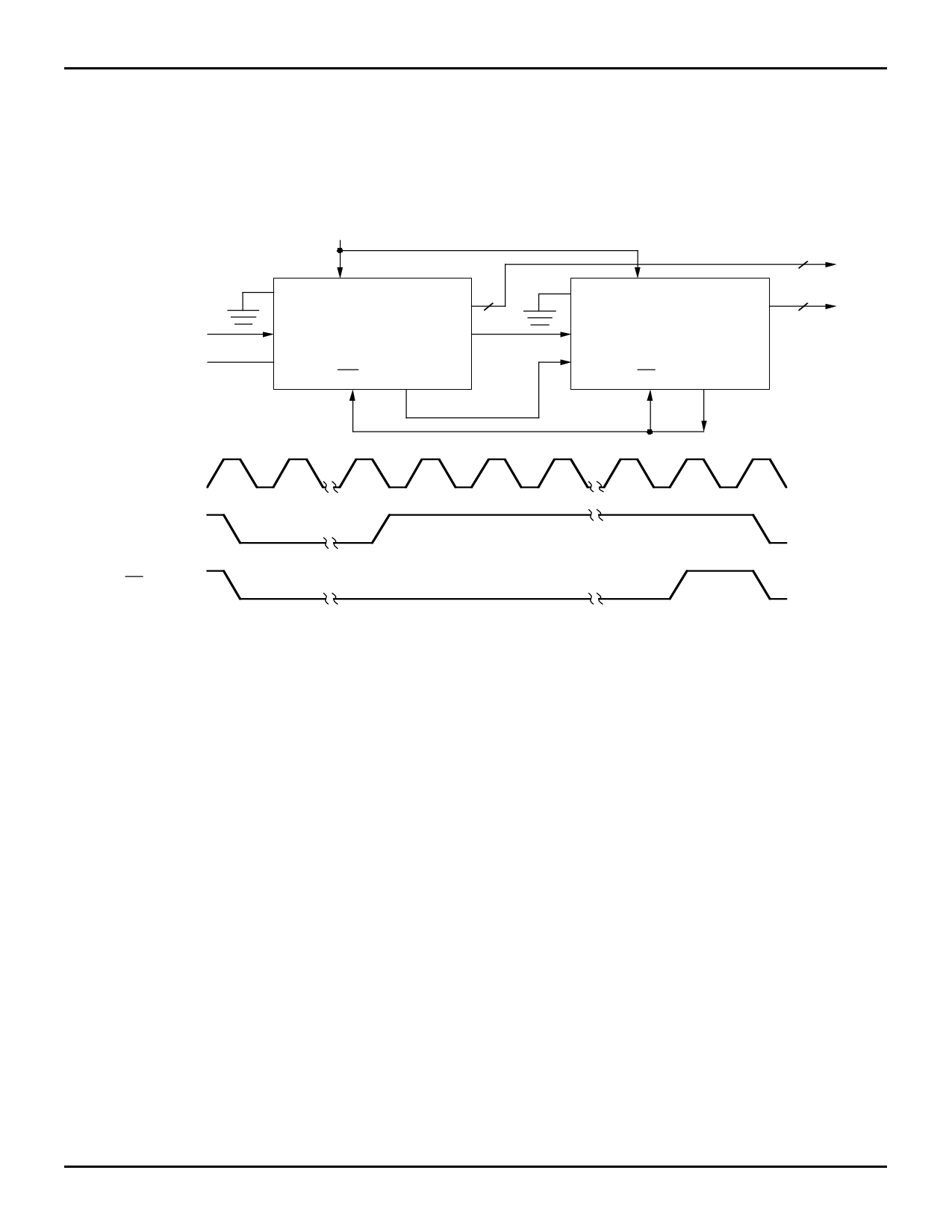

Width Expansion Configuration

In the cascaded case, word widths of more than 9 bits can

be achieved by using more than one device. By tying the SIX

line of the least significant device HIGH and the SIX of the

subsequent devices to the appropriate Data Set lines of the

previous devices, a cascaded serial word is achieved.

On the first LOW-to-HIGH clock edge of SICP, both the

Data Set lines go LOW. Just as in the standalone case, on

each corresponding clock cycle, the equivalent Data Set line

goes HIGH in order of least to most significant.

SERIAL-IN CLOCK

VCC

SERIAL DATA IN

XI SI

8

Q 0-7

SICP

FIFO #1

SIX

NW

D7

8

XI

SI

SICP

FIFO #2

Q 0-7

PARALLEL

DATA OUT

8

SIX

NW

D7

0

SOCP

D 7 OF FIFO #1

AND SIX OF

FIFO #2

D 7 OF FIFO #2

AND NW TO

FIFO #1 AND

FIFO #2

1

7

8

9

10

14

15

Figure 14. Serial-In to Parallel-Out Data of 16 Bits

0

2752 drw 17

5.36

11