IDT723613L30PQF Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT723613L30PQF

IDT723613L30PQF Datasheet PDF : 29 Pages

| |||

IDT723613 CMOS CLOCKED FIFO WITH BUS MATCHING AND BYTE SWAPPING

64 x 36

COMMERCIAL TEMPERATURE RANGES

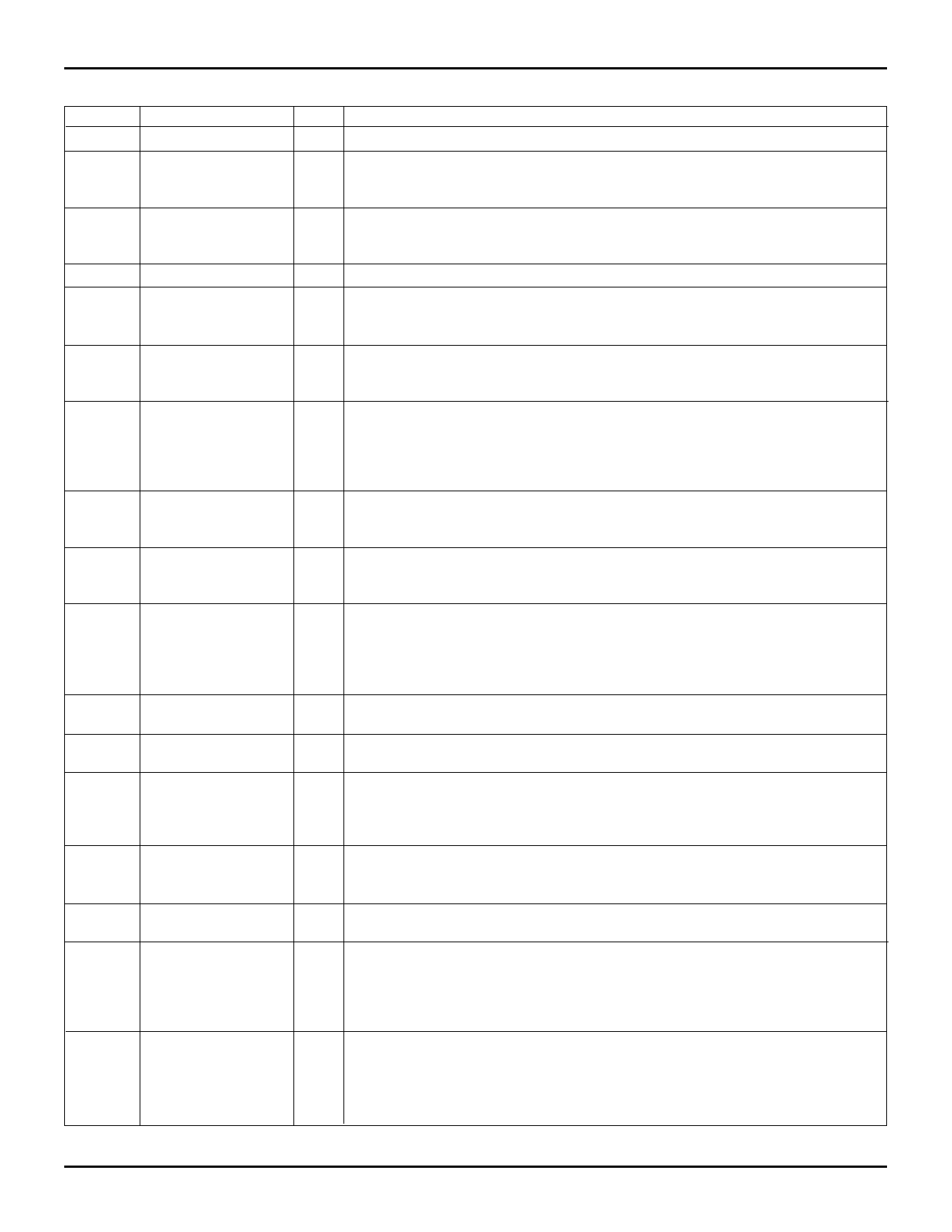

PIN DESCRIPTION

Symbol

Name

I/O

Description

A0-A35

AE

AF

Port A Data

Almost-Empty Flag

Almost-Full Flag

I/O

O

Port B

O

Port A

36-bit bidirectional data port for side A.

Programmable almost-empty flag synchronized to CLKB. It is LOW when

Port B the number of 36-bit words in the FIFO is less than or equal to the value

in the offset register, X.

Programmable almost-full flag synchronized to CLKA. It is LOW when the

number of 36-bit empty locations in the FIFO is less than or equal to the value in

the offset register, X.

B0-B35

BE

Port B Data

Big-Endian Select

I/O 36-bit bidirectional data port for side B

I Selects the bytes on port B used during byte or word FIFO reads. A LOW on

BE selects the most significant bytes on B0-B35 for use, and a HIGH selects

the least significant bytes.

CLKA

Port A Clock

I CLKA is a continuous clock that synchronizes all data transfers through port A

and can be asynchronous or coincident to CLKB. FF and AF are synchronized

to the LOW-to-HIGH transition of CLKA.

CLKB

CSA

CSB

EF

Port B Clock

Port A Chip Select

Port B Chip Select

Empty Flag

I CLKB is a continuous clock that synchronizes all data transfers through port B

and can be asynchronous or coincident to CLKA. Port-B byte swapping and

data port sizing operations are also synchronous to the LOW-to-HIGH transi-

tion of CLKB. EF and AE are synchronized to the LOW-to-HIGH transition of

CLKB.

I CSA must be LOW to enable a LOW-to-HIGH transition of CLKA to read or

write data on port A. The A0-A35 outputs are in the high-impedance state

when CSA is HIGH.

I CSB must be LOW to enable a LOW-to-HIGH transition of CLKB to read or

write data on port B. The B0-B35 outputs are in the high-impedance state

when CSB is HIGH.

O EF is synchronized to the LOW-to-HIGH transition of CLKB. When EF is LOW,

Port B the FIFO is empty, and reads from its memory are disabled. Data can be read

from the FIFO to its output register when EF is HIGH. EF is forced LOW when

the device is reset and is set HIGH by the second LOW-to-HIGH transition of

CLKB after data is loaded into empty FIFO memory.

ENA

Port A Enable

I ENA must be HIGH to enable a LOW-to-HIGH transition of CLKA to read or

write data on port A.

ENB

FF

FS1, FS0

Port B Enable

Full Flag

Flag Offset Selects

I

O

Port A

I

ENB must be HIGH to enable a LOW-to-HIGH transition of CLKB to read or

write data on port B.

FF is synchronized to the LOW-to-HIGH transition of CLKA. When FF is LOW,

the FIFO is full, and writes to its memory are disabled. FF is forced LOW when

the device is reset and is set HIGH by the second LOW-to-HIGH transition of

CLKA after reset.

The LOW-to-HIGH transition of RST latches the values of FS0 and FS1,

which loads one of four preset values into the almost-full flag and almost-empty

flag offsets.

MBA

MBF1

MBF2

Port A Mailbox Select I

Mail1 Register Flag O

Mail2 Register Flag O

A high level on MBA chooses a mailbox register for a port A read or write

operation. When the A0-A35 outputs are active, mail2 register data is output.

MBF1 is set LOW by a LOW-to-HIGH transition of CLKA that writes data to

the mail1 register. Writes to the mail1 register are inhibited while MBF1 is set

LOW. MBF1 is set HIGH by a LOW-to-HIGH transition of CLKB when a

port B read is selected and both SIZ1 and SIZ0 are HIGH. MBF1 is set HIGH

when the device is reset.

MBF2 is set LOW by a LOW-to-HIGH transition of CLKB that writes data to

the mail2 register. Writes to the mail2 register are inhibited while MBF2 is set

LOW. MBF2 is set HIGH by a LOW-to-HIGH transition of CLKA when a

port A read is selected and MBA is HIGH. MBF2 is set HIGH when the device

is reset.

4