STK12C68-5 Просмотр технического описания (PDF) - Cypress Semiconductor

Номер в каталоге

Компоненты Описание

Список матч

STK12C68-5 Datasheet PDF : 18 Pages

| |||

STK12C68-5 (SMD5962-94599)

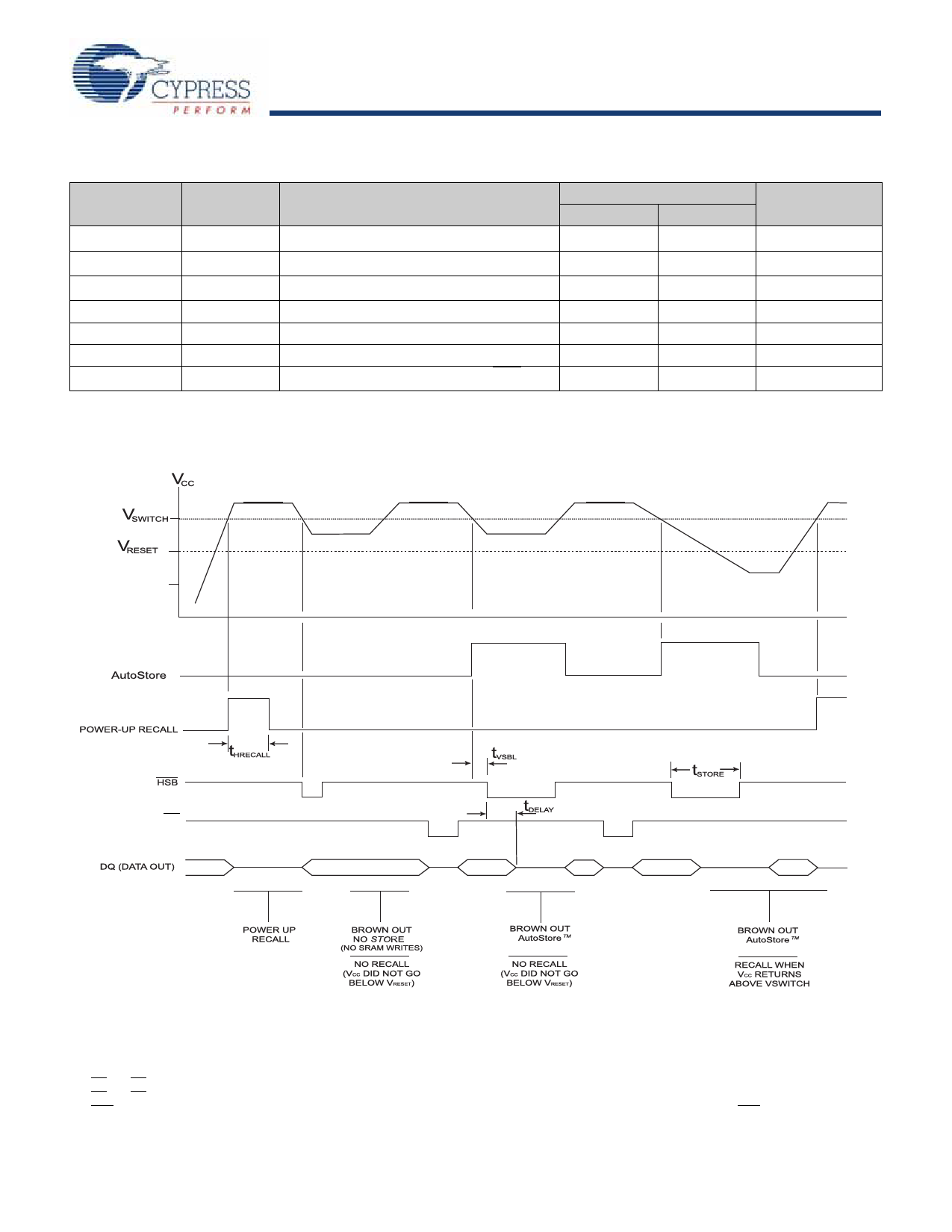

AutoStore or Power Up RECALL

Parameter

Alt

tHRECALL [13]

tSTORE [14, 15, 16]

tDELAY [9, 15]

VSWITCH

VRESET

tVCCRISE

tVSBL[11]

tRESTORE

tHLHZ

tHLQZ , tBLQZ

Switching Waveform

Description

Power up RECALL Duration

STORE Cycle Duration

Time Allowed to Complete SRAM Cycle

Low Voltage Trigger Level

Low Voltage Reset Level

VCC Rise Time

Low Voltage Trigger (VSWITCH) to HSB Low

STK12C68-5

Min

Max

550

10

1

4.0

4.5

3.9

150

300

Figure 12. AutoStore/Power Up RECALL

Unit

μs

ms

μs

V

V

μs

ns

WE

Notes

13. tHRECALL starts from the time VCC rises above VSWITCH.

14. CE and OE low for output behavior.

15. CE and OE low and WE high for output behavior.

16. HSB is asserted low for 1us when VCAP drops through VSWITCH. If an SRAM Write has not taken place since the last nonvolatile cycle, HSB is released and no store

takes place.

Document Number: 001-51026 Rev. **

Page 11 of 18

[+] Feedback