SM5168 Просмотр технического описания (PDF) - Nippon Precision Circuits

Номер в каталоге

Компоненты Описание

Список матч

SM5168 Datasheet PDF : 9 Pages

| |||

SM5168 series

FUNCTIONAL DESCRIPTION

SM5168A× series

Frequency dividers

The comparator frequency divider (N-counter) and reference frequency divider (R-counter), one of each, are

set in master-slice to the following values.

I Comparator frequency divider (N-counter) = 272 to 65535

I Reference frequency divider (R-counter) = 5 to 65535

Standby mode

When OPR goes from HIGH to LOW, the PLL is in standby mode with the following input/output conditions.

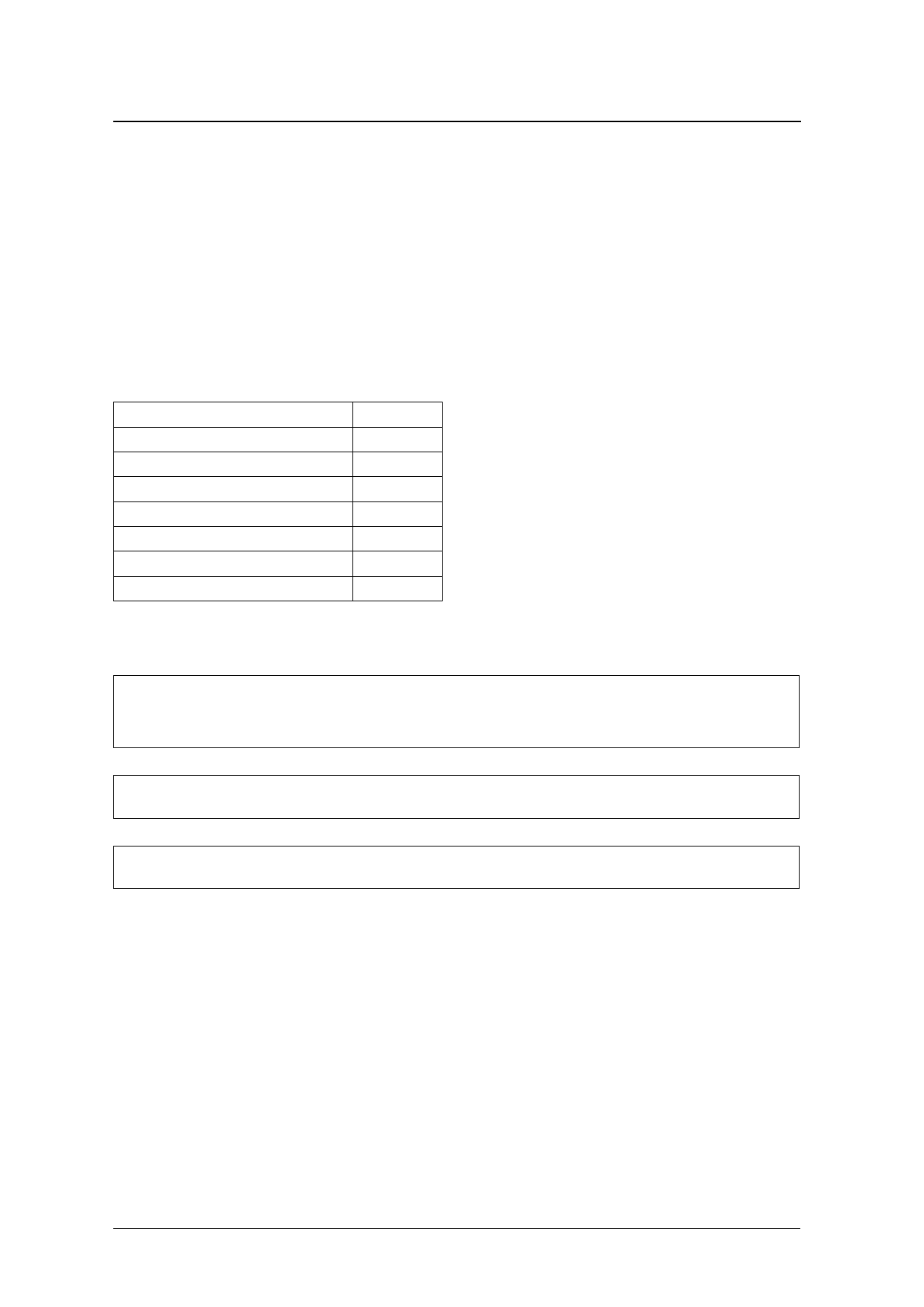

Block

Input FIN

Comparator frequency divider (N-counter)

Input XIN

Reference frequency divider (R-counter)

Phase comparator

Output DO

Output LD

State

LOW level

Stopped

LOW level

Stopped

Reset

Floating

LOW-level

When OPR goes from LOW to HIGH, standby mode is released and the PLL is in operating mode, and the fol-

lowing start-up sequence is executed.

Internal feedback resistance is connected to XIN to activate the reference frequency divider (R-counter).

Internal feedback resistance is connected to FIN.

The comparator frequency divider (N-counter) and the phase comparator are reset.

DO is floating and LD is LOW.

↓

Reference frequency divider (R-counter) starts to perform frequency division.

An internal signal (FR signal) is output on the 2nd clock cycle.

↓

Phase comparator starts and comparator frequency divider (N-counter) starts to perform frequency division.

DO floating condition is released and LD goes HIGH.

SEIKO NPC CORPORATION —6