MX93002 Просмотр технического описания (PDF) - Macronix International

Номер в каталоге

Компоненты Описание

Список матч

MX93002 Datasheet PDF : 35 Pages

| |||

MX93002

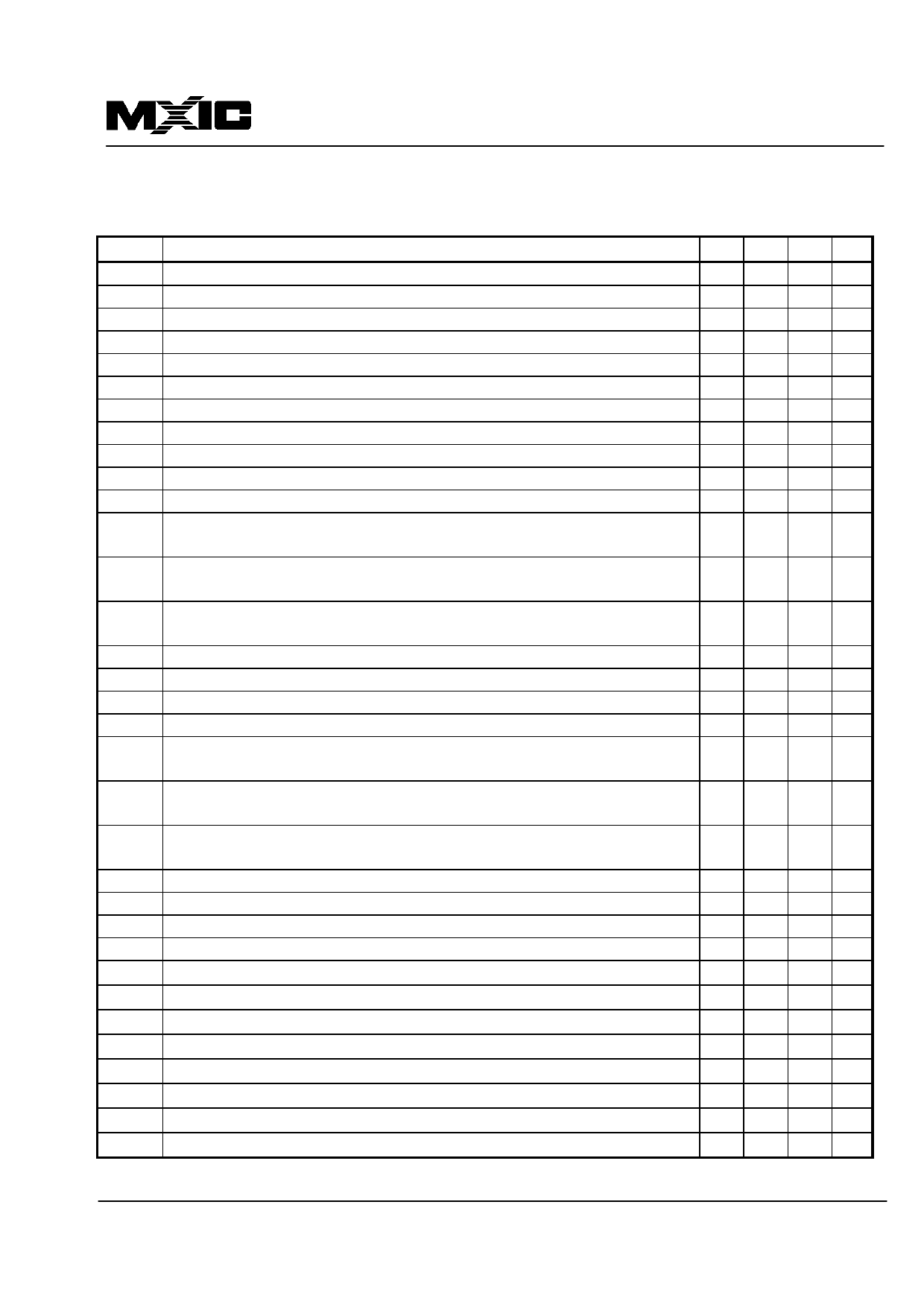

TIMING DESCRIPTION

TIMING

DESCRIPTION

MIN TYP MAX UNIT

1/Tmck frequency of master clock (from Vmckh1 to next Vmckh1) at RATE = 0

1.638 2.048 2.560 MHz

Trmck rise time of master clock

50 ns

Tfmck fall time of master clock

50 ns

Tfs from Vmckh1 to Vfsh1

0

ns

Tfsh holding time for frame sync. From Vfsh1 to Vfsh2

MCLK

ns

Tdxs setting time for CODEC transmit data from Vmckh1(n) to DX(n) data ready 110

ns

Tdrh1 holding time for CODEC received data from DR(n) data ready to Vmckh2(n) 0

ns

Tdrh2 holding time for CODEC received data from Vmckl(n) to DR(n) ending

150

ns

Tupen1 from Vsclkh1 to Venl

40

Tupen2 from Vsclkh1 to Venh

40

Tups1 setting time for uP transmitting SDATA from Vupenl to uP SDATA(n) ready 40

( @ where Tupen1+Tups1 must < SCLK )

Tups2 setting time for uP transmitting SDATA from Vsclkh1(n+1) to uP

40

SDATA(n+1) ready

Tuph holding time for uP transmitting SDATA from Vsclkh1(n+1) to uP SDATA(n) 40

ending

Tcdrd from Vsclkh1(n+1) to CODEC reading SDATA(n)

SCLK ns

SCLK ns

SLCK ns

SCLK ns

Tups2 ns

20 ns

Tupo2i from Vupenl to uP changing its SDATA interface to input port

40

Tcdi2o from Vsclkh1 to CODEC changing its SDATA interface to output port

Tcds1 setting time for CODEC transmitting SDATA from Vcdi2o to SDATA(n)

ready

Tcds2 setting time for CODEC transmitting SDATA from Vsclkh1(n+2) to

SDATA(n+1) ready

Tcdh holding time for CODEC transmitting SDATA from SDATA(n) ready to

Vsclkh1(n+2)

Tcdo2i from Venh to CODEC changing its SDATA interface to input port

Tuprd from Vsclkh1(n+1) to uP reading SDATA(n)

40

Tupi2o from Vsclkh1 to uP changing its SDATA interface to output port

40

FS ns

20 ns

20 ns

20 ns

SCLK ns

20 ns

SCLK ns

FS ns

Vmckh1 logic high when CODEC MCLK rising

Vmckh2 logic high when CODEC MCLK falling

Vmckl logic low when CODEC MCLK falling

Vfsh1 logic high when CODEC FS rising

Vsclkh1 logic high when SCLK rising

Vcdi2o CODEC changes its SDATA interface to output port

Venh logic high when uP SDENB rising

Venl logic low when uP SDENB falling

19