IDT821068 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT821068 Datasheet PDF : 45 Pages

| |||

IDT821068 OCTAL PROGRAMMABLE PCM CODEC

INDUSTRIAL TEMPERATURE RANGE

C/I CHANNEL

In both compressed GCI and linear GCI mode, the upstream and

downstream C/I channel bytes are continuously carrying I/O information

every frame to and from the IDT821068. In this way, the upstream

processor can have an immediate access to SLIC output data present

on IDT821068’s programmable I/O port on SLIC side through

downstream C/I channel, as well as to SLIC input data through upstream

C/I channel. The IDT821068 transmits or receives the C/I channel data

with the Most Significant Bit first.

The MR and MX bits are used for handshaking during data

exchanges on the monitor channel.

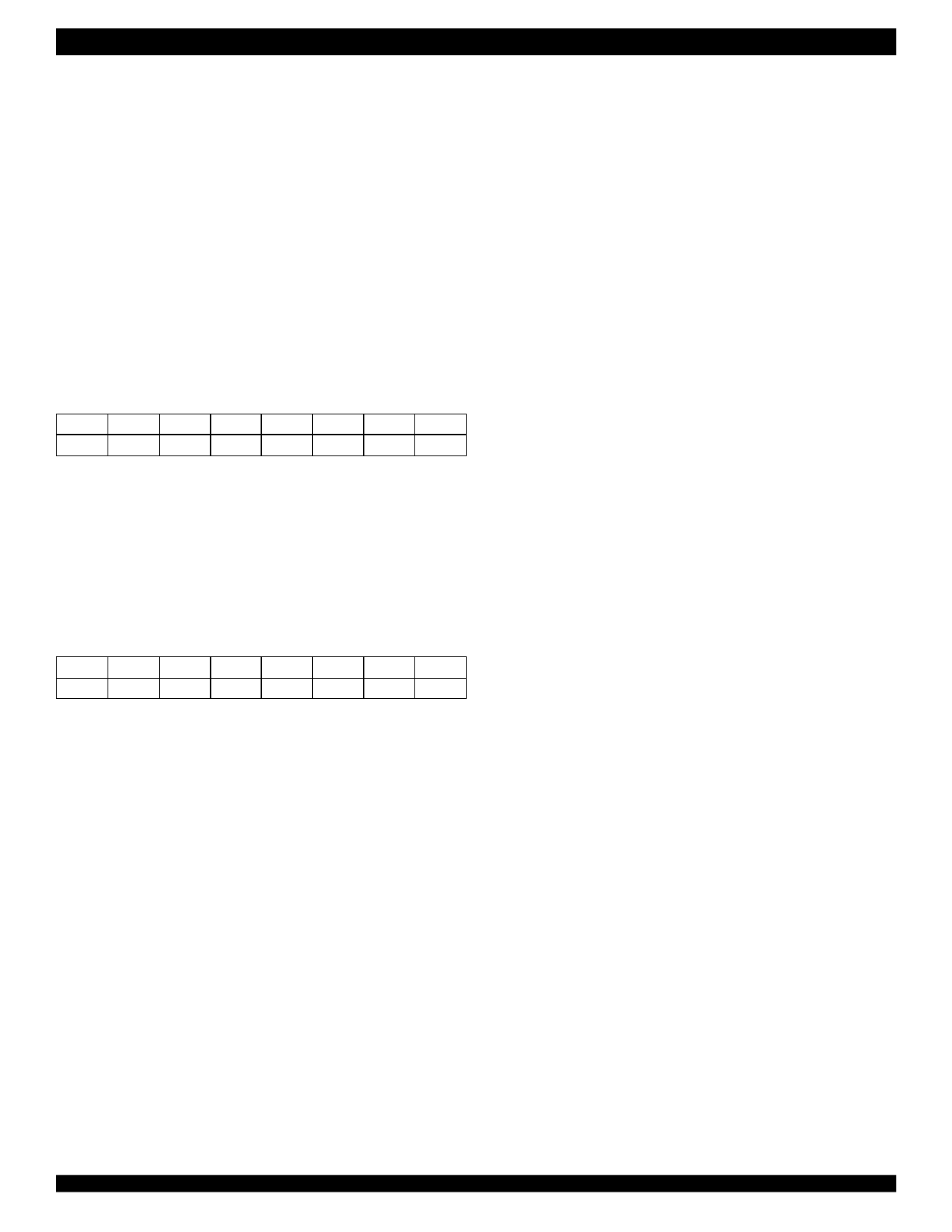

Upstream C/I Channel

The C/I channel which includes six C/I channel bits, is transmitted

upstream by the IDT821068 every frame. The bit definitions for the

upstream C/I channel are shown below.

Upstream C/I Octet

MSB

LSB

b7

b6

b5

b4

b3

b2

b1

b0

SI1(A) SI2(A) SB1(A) SI1(B) SI2(B) SB1(B) MR MX

The logic state of input ports SI1 and SI2 for channel A and channel B,

as well as the bidirectional port SB1 for channel A and B if SB1 is

programmed as an input, are read and transmitted in the upstream C/I

channel. When SB2 is programmed as input, its data are not available in

upstream C/I channel and can be read by Global Command 12 only.

Downstream C/I Channel

The downstream C/I octet is defined as:

Downstream C/I Octet

MSB

LSB

b7

b6

b5

b4

b3

b2

b1

b0

A/B SO3 SO2 SO1 SB1 SB2 M R M X

Herein, A/B selects channel A or Channel B:

A/B = 0: channel A is selected; A/B = 1: channel B is selected.

The downstream C/I channel carries the SLIC output data bits of

SO1, SO2 and SO2 for channel A or B, as well as SB1 and SB2 output

bits when SB1 and SB2 are programmed as outputs.

MONITOR CHANNEL

The monitor channel is used to transfer of maintenance information

between the upstream and downstream devices. The information

includes reading/writing the global/local registers and coefficient/FSK

RAM of the IDT821068 or providing SLIC signaling and so on. Using

two monitor control bits (MR and MX) per direction, data is transferred

in a complete handshake procedure. The MR and MX bits in the C/I

Channel of the GCI frame are used for the handshake procedure of

the monitor channel. See Figure 6.

The monitor channel transmission operates on a pseudo-

asynchronous basis:

- Data transfer (bits) on the bus is synchronized to FSC;

- Data flow (bytes) are asynchronously controlled by the handshake

procedure.

For example: Data is placed onto the DD Monitor Channel by the

Monitor Transmitter of the master device (DD MX bit is activated and

set to ‘0’). This data transfer will be repeated within each frame (125

µs rate) until it is acknowledged by the IDT821068 Monitor Receiver

by setting the DU MR bit to ‘0’, which is checked by the Monitor

Transmitter of the master device. Thus, the data rate is not 8 kbytes/s.

Monitor Handshake

The monitor channel works in 3 states:

I. Idle state: A pair of inactive (set to ‘1’) MR and MX bits during two

or more consecutive frames shows an idle state on the monitor

channel and the End of Message (EOM);

II. Sending state: MX bit is activated (set to ‘0’) by the Monitor

Transmitter, together with data-bytes (can be changed) on the monitor

channel;

III. Acknowledging: MR bit is set to active (i.e. ‘0’) by the Monitor

Receiver, together with a data byte remaining in the monitor channel.

A start of transmission is initiated by a monitor transmitter by

sending out an active MX bit together with the first byte of data to be

transmitted in the monitor channel. This state remains until the

addressed monitor receiver acknowledges the receipt by sending out

an active low MR bit. The data transmission is repeated each 125 µs

frame (minimum is one repetition). During this time the Monitor

Transmitter keeps evaluating the MR bit.

Flow control, means in the form of transmission delay, can only take

place when the transmitters MX and the receivers MR bit are in active

state.

Since the receiver is able to receive the monitor data at least twice

(in two consecutive frames), it is able to check for data errors. If two

different bytes are received the receiver will wait for the receipt of two

identical successive bytes (last look function).

A collision resolution mechanism (check if another device is trying

to send data during the same time) is implemented in the transmitter.

This is done by looking for the inactive (‘1’) phase of the MX bit and

making a per bit collision check on the transmitted monitor data

(check if transmitted ‘1’s are on DU/DD line; DU/DD line are open

drain lines).

Any abort leads to a reset of the IDT821068 command stack, the

device is ready to receive new commands.

To obtain a maximum speed data transfer, the transmitter

anticipates the falling edge of the receivers acknowledgment.

Due to the inherent programming structure, duplex operation is not

possible. It is not allowed to send any data to the IDT821068, while

transmission is active.

Refer to Figure 7 and 8 for more information about monitor

handshake procedure.

The IDT821068 can be controlled very flexibly by commands

operating on registers or RAMs via the GCI monitor channel, refer to

“Programming Description” for further details.

9