IDT72V3622(2015) Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72V3622

(Rev.:2015)

(Rev.:2015)

IDT72V3622 Datasheet PDF : 29 Pages

| |||

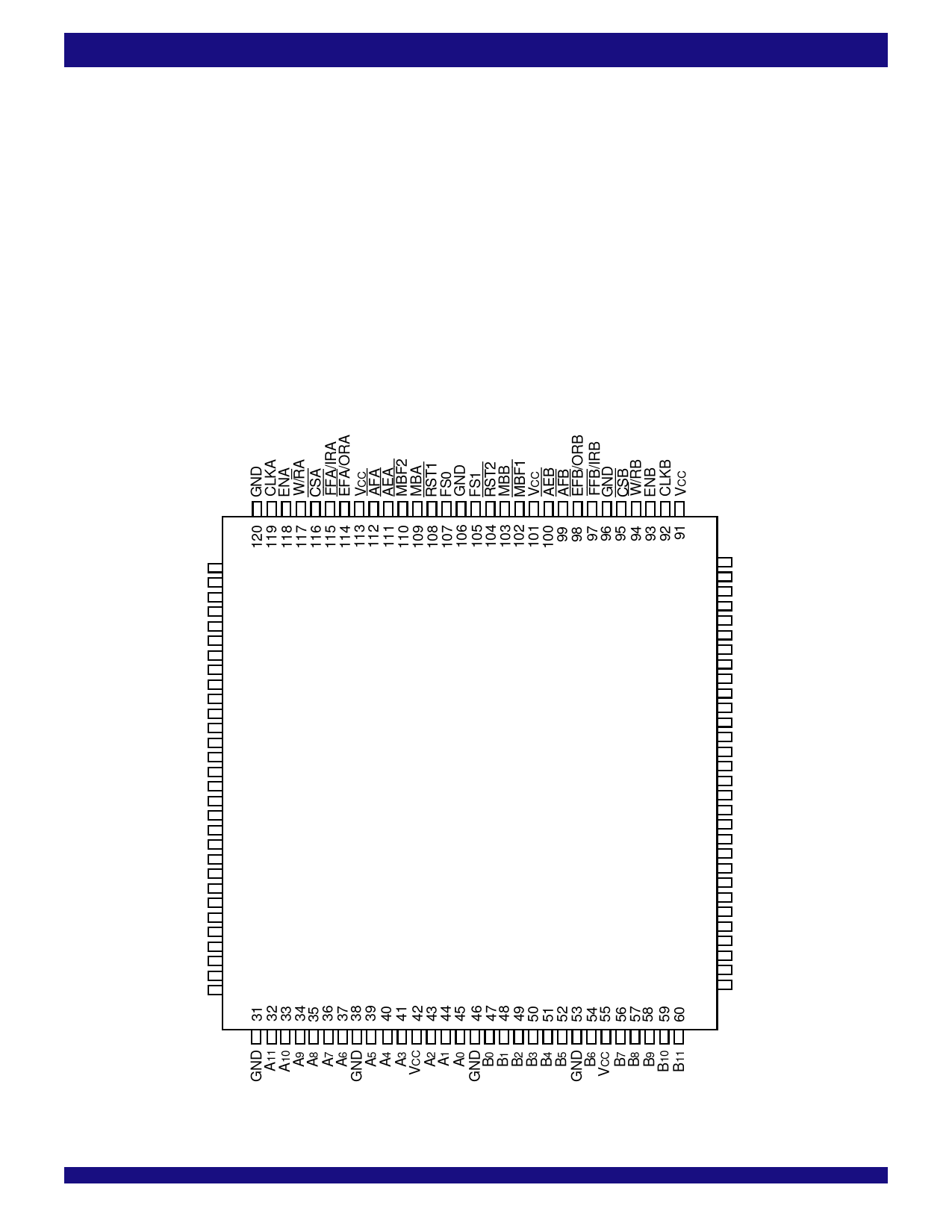

IDT72V3622/72V3632/72V3642 CMOS 3.3V SyncBiFIFOTM

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

These devices have two modes of operation: In the IDT Standard mode,

the first word written to an empty FIFO is deposited into the memory array. A

read operation is required to access that word (along with all other words

residing in memory). In the First Word Fall Through mode (FWFT), the first long-

word (36-bit wide) written to an empty FIFO appears automatically on the

outputs, no read operation required (Nevertheless, accessing subsequent

words does necessitate a formal read request). The state of the FWFT pin during

FIFO operation determines the mode in use.

Each FIFO has a combined Empty/Output Ready Flag (EFA/ORA and

EFB/ORB) and a combined Full/Input Ready Flag (FFA/IRA and FFB/IRB).

The EF and FF functions are selected in the IDT Standard mode. EF indicates

whether or not the FIFO memory is empty. FF shows whether the memory is

full or not. The IR and OR functions are selected in the First Word Fall Through

mode. IR indicates whether or not the FIFO has available memory locations.

OR shows whether the FIFO has data available for reading or not. It marks the

presence of valid data on the outputs.

Each FIFO has a programmable Almost-Empty flag (AEA and AEB) and

a programmable Almost-Full flag (AFA and AFB). AEA and AEB indicate when

COMMERCIAL TEMPERATURE RANGE

a selected number of words remain in the FIFO memory. AFA and AFB indicate

when the FIFO contains more than a selected number of words.

FFA/IRA, FFB/IRB, AFA and AFB are two-stage synchronized to the port

clock that writes data into its array. EFA/ORA, EFB/ORB, AEA and AEB are

two-stage synchronized to the port clock that reads data from its array.

Programmable offsets for AEA, AEB, AFA and AFB are loaded by using Port

A. Three default offset settings are also provided. The AEA and AEB threshold

can be set at 8, 16 or 64 locations from the empty boundary and the AFA and

AFB threshold can be set at 8, 16 or 64 locations from the full boundary. All these

choices are made using the FS0 and FS1 inputs during Reset.

Two or more devices may be used in parallel to create wider data paths.

If, at any time, the FIFO is not actively performing a function, the chip will

automatically power down. During the power down state, supply current

consumption (ICC) is at a minimum. Initiating any operation (by activating control

inputs) will immediately take the device out of the power down state.

The IDT72V3622/72V3632/72V3642 are characterized for operation from

0oC to 70oC. Industrial temperature range (-40οC to +85οC) is available by

special order. They are fabricated using high speed, submicron CMOS

technology.

3