IDT72V3612 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72V3612 Datasheet PDF : 25 Pages

| |||

IDT72V3612 3.3V, CMOS SyncBiFIFOTM

64 x 36 x 2

COMMERCIAL TEMPERATURE RANGE

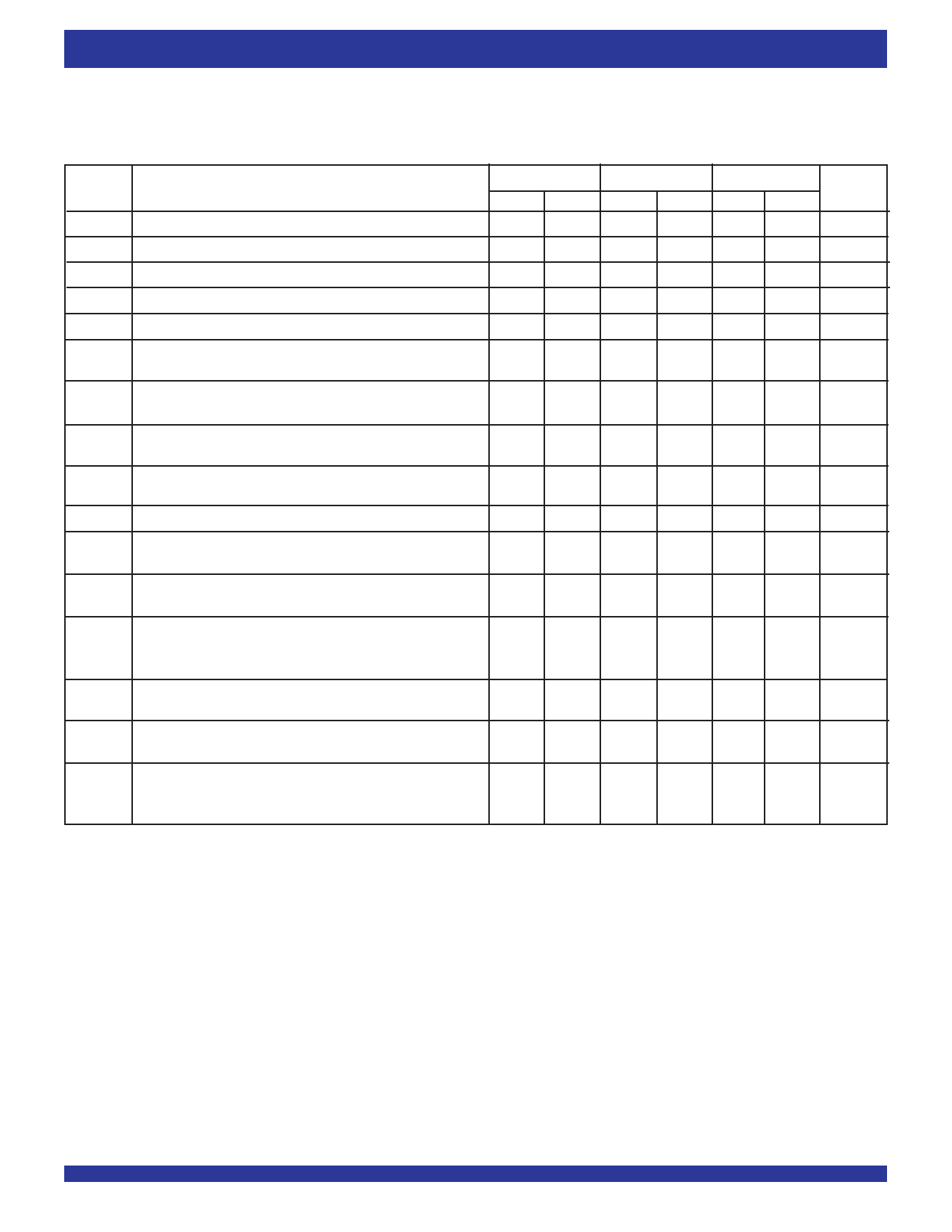

SWITCHING CHARACTERISTICS OVER RECOMMENDED RANGES OF

SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE, CL = 30pF

Commercial: Vcc=3.3V± 0.30V; for 12ns (83MHz) operation, Vcc=3.3V ±0.15V; TA = 0°C to +70°C; JEDEC JESD8-A compliant

Symbol

Parameter

IDT72V3612L12 IDT72V3612L15 IDT72V3612L20

Min. Max. Min. Max. Min. Max. Unit

tA

Access Time, CLKA↑ to A0-A35 and CLKB↑ to B0-B35

1

8

2

10

2

12

ns

tWFF

Propagation Delay Time, CLKA↑ to FFA and CLKB↑ to FFB

1

8

2

10

2

12

ns

tREF

Propagation Delay Time, CLKA↑ to EFA and CLKB↑ to EFB

1

8

2

10

2

12

ns

tPAE

Propagation Delay Time, CLKA↑ to AEA and CLKB↑ to AEB

1

8

2

10

2

12

ns

tPAF

Propagation Delay Time, CLKA↑ to AFA and CLKB↑ to AFB

1

8

2

10

2

12

ns

tPMF

Propagation Delay Time, CLKA↑ to MBF1 LOW or MBF2

HIGH and CLKB↑ to MBF2 LOW or MBF1 HIGH

1

8

1

9

1

12

ns

tPMR

Propagation Delay Time, CLKA↑ to B0-B35(1) and CLKB↑

to A0-A35(2)

2

8

2

10

2

12

ns

tMDV

Propagation Delay Time, MBA to A0-A35 valid and MBB to

B0-B35 valid

1

8

1

10

1 11.5

ns

tPDPE Propagation Delay Time, A0-A35 valid to PEFA valid; B0-B35

2

8

2

10

2

11

ns

valid to PEFB valid

tPOPE Propagation Delay Time, ODD/EVEN to PEFA and PEFB

2

8

2

10

2

12

ns

tPOPB(3) Propagation Delay Time, ODD/EVEN to parity bits (A8, A17,

2

8

2

10

2

12

ns

A26, A35) and (B8, B17, B26, B35)

tPEPE Propagation Delay Time, W/RA, CSA, ENA, MBA or PGA to

1

8

1

10

1

12

ns

PEFA; W/RB, CSB, ENB. MBB, PGB to PEFB

tPEPB(3) Propagation Delay Time, W/RA, CSA, ENA, MBA or PGA to

2

8

2

10

2

12

ns

parity bits (A8, A17, A26, A35); W/RB, CSB, ENB. MBB or PGB

to parity bits (B8, B17, B26, B35)

tRSF

Propagation Delay Time, RST to (AEA, AEB) LOW and

(AFA, AFB, MBF1, MBF2) HIGH

1

10

1

15

1

20

ns

tEN

Enable Time, CSA and W/RA LOW to A0-A35 active and

CSB LOW and W/RB HIGH to B0-B35 active

2

6

2

10

2

12

ns

tDIS

Disable Time, CSA or W/RA HIGH to A0-A35 at high-

impedance and CSB HIGH or W/RB LOW to B0-B35 at

high impedance

1

6

1

8

1

9

ns

NOTES:

1. Writing data to the mail1 register when the B0-B35 outputs are active and MBB is HIGH.

2. Writing data to the mail2 register when the A0-A35 outputs are active and MBA is HIGH.

3. Only applies when reading data from a mail register.

9