IDT723613L20PF Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT723613L20PF

IDT723613L20PF Datasheet PDF : 26 Pages

| |||

IDT723613 CMOS CLOCKED FIFO WITH

BUS-MATCHING AND BYTE SWAPPING 64 x 36

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

FUNCTIONAL DESCRIPTION

RESET (RST)

The IDT723613 is reset by taking the Reset (RST) input LOW for at least four

port A Clock (CLKA) and four port B Clock (CLKB) LOW-to-HIGH transitions.

The Reset input can switch asynchronously to the clocks. A device reset

initializes the internal read and write pointers of the FIFO and forces the Full Flag

(FF) LOW, the Empty Flag (EF) LOW, the Almost-Empty flag (AE) LOW, and

the Almost-Full flag (AF) HIGH. A reset also forces the Mailbox Flags (MBF1,

MBF2) HIGH. After a reset, FF is set HIGH after two LOW-to-HIGH transitions

of CLKA. The device must be reset after power up before data is written to its

memory.

A LOW-to-HIGH transition on the RST input loads the Almost-Full and Almost-

Empty Offset register (X) with the value selected by the Flag Select (FS0, FS1)

inputs. The values that can be loaded into the register are shown in Table 1.

FIFO WRITE/READ OPERATION

The state of the port A data (A0-A35) outputs is controlled by the port-A Chip

Select (CSA) and the port-A Write/Read select (W/RA). The A0-A35 outputs are

in the high-impedance state when either CSA or W/RA is HIGH. The A0-A35

outputs are active when both CSA and W/RA are LOW.

Data is loaded into the FIFO from the A0-A35 inputs on a LOW-to-HIGH

transition of CLKA when CSA is LOW, W/RA is HIGH, ENA is HIGH, MBA is

LOW, and FFA is HIGH (see Table 2).

The state of the port B data (B0-B35) outputs is controlled by the port B Chip

Select (CSB) and the port B Write/Read select (W/RB). The B0-B35 outputs are

in the high-impedance state when either CSB or W/RB is HIGH. The B0-B35

outputs are active when both CSB and W/RB are LOW. Data is read from the

FIFO to the B0-B35 outputs by a LOW-to-HIGH transition of CLKB when CSB

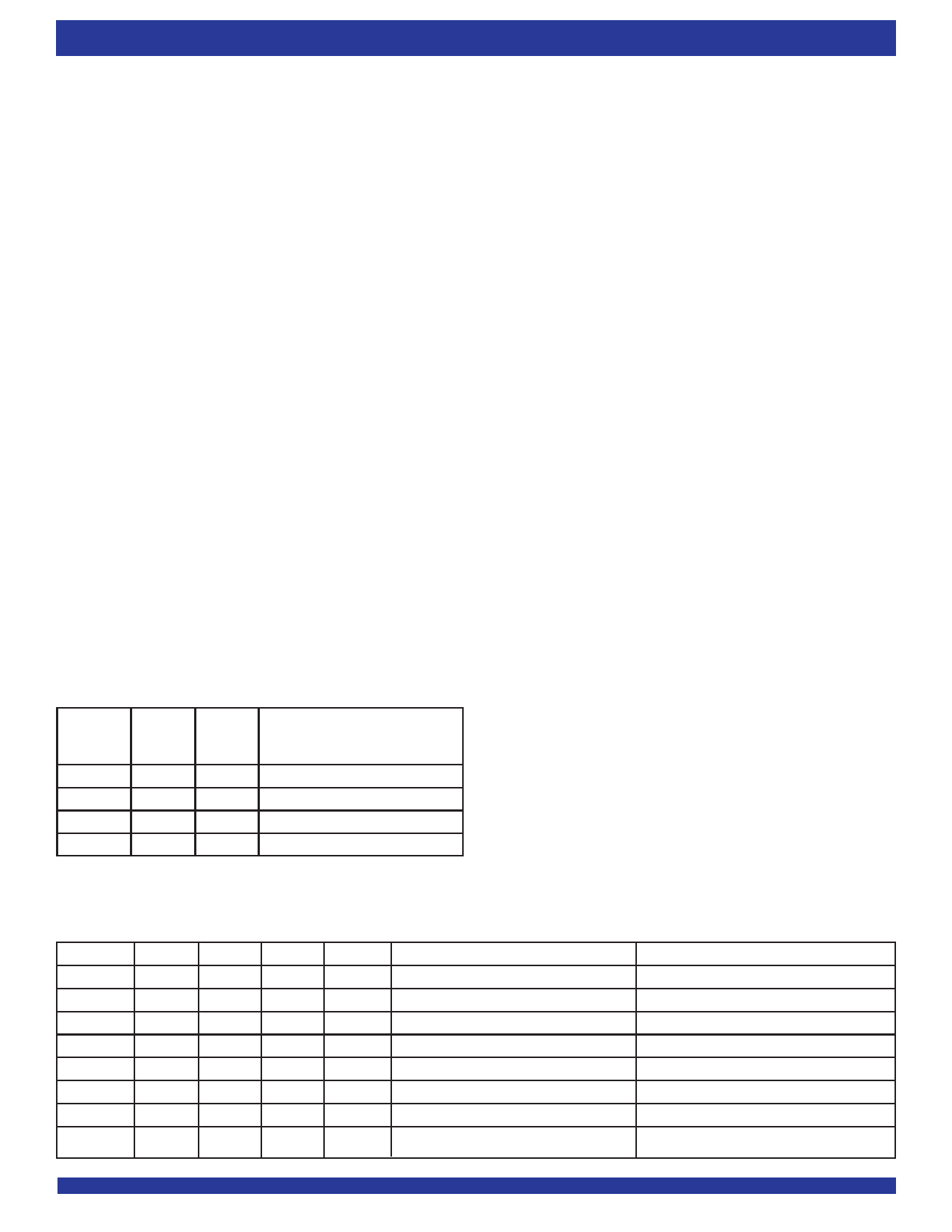

TABLE 1 — FLAG PROGRAMMING

FS1

FS0

RST

H

H

↑

H

L

↑

L

H

↑

L

L

↑

Almost-Full and

Almost-Empty Flag

Offset Register (X)

16

12

8

4

is LOW, W/RB is LOW, ENB is HIGH, EFB is HIGH, and either SIZ0 or SIZ1

is LOW (see Table 3).

The setup and hold-time constraints to the port clocks for the port Chip Selects

(CSA, CSB) and Write/Read selects (W/RA, W/RB) are only for enabling write

and read operations and are not related to high-impedance control of the data

outputs. If a port enable is LOW during a clock cycle, the port’s Chip Select and

Write/Read select can change states during the setup and hold time window of

the cycle.

SYNCHRONIZED FIFO FLAGS

Each FIFO flag is synchronized to its port clock through two flip-flop stages.

This is done to improve the flags’ reliability by reducing the probability of

metastable events on their outputs when CLKA and CLKB operate asynchro-

nously to one another. FF and AF are synchronized to CLKA. EF and AE are

synchronized to CLKB. Table 4 shows the relationship of each port flag to the

level of FIFO fill.

EMPTY FLAG (EF)

The FIFO Empty Flag is synchronized to the port clock that reads data from

its array (CLKB). When the EF is HIGH, new data can be read to the FIFO output

register. When the EF is LOW, the FIFO is empty and attempted FIFO reads

are ignored. When reading the FIFO with a byte or word size on port B, EF is

set LOW when the fourth byte or second word of the last long word is read.

The FIFO read pointer is incremented each time a new word is clocked to

its output register. The state machine that controls the EF monitors a write-pointer

and read-pointer comparator that indicates when the FIFO SRAM status is

empty, empty+1, or empty+2. A word written to the FIFO can be read to the

FIFO output register in a minimum of three port B clock (CLKB) cycles.

Therefore, an EF is LOW if a word in memory is the next data to be sent to the

FIFO output register and two CLKB cycles have not elapsed since the time the

word was written. The EF of the FIFO is set HIGH by the second LOW-to-HIGH

transition of CLKB, and the new data word can be read to the FIFO output register

in the following cycle.

A LOW-to-HIGH transition on CLKB begins the first synchronization cycle of

a write if the clock transition occurs at time tSKEW1 or greater after the write.

Otherwise, the subsequent CLKB cycle can be the first synchronization cycle

(see Figure 10).

FULL FLAG (FF)

The FIFO Full Flag is synchronized to the port clock that writes data to its array

TABLE 2 — PORT A ENABLE FUNCTION TABLE

CSA

W/RA

ENA

MBA CLKA

A0-A35 Outputs

H

X

X

X

X

In high-impedance state

L

H

L

X

X

In high-impedance state

L

H

H

L

↑

In high-impedance state

L

H

H

H

↑

In high impedance state

L

L

L

L

X

Active, mail2 register

L

L

H

L

↑

Active, mail2 register

L

L

L

H

X

Active, mail2 register

L

L

H

H

↑

Active, mail2 register

10

Port Function

None

None

FIFO write

Mail1 write

None

None

TEMNPonEeRATURE RANGES

Mail2 read (set MBF2 HIGH)

JANUARY 14, 2009