ICS9148-11 Просмотр технического описания (PDF) - Integrated Circuit Systems

Номер в каталоге

Компоненты Описание

Список матч

ICS9148-11 Datasheet PDF : 14 Pages

| |||

ICS9148 - 11

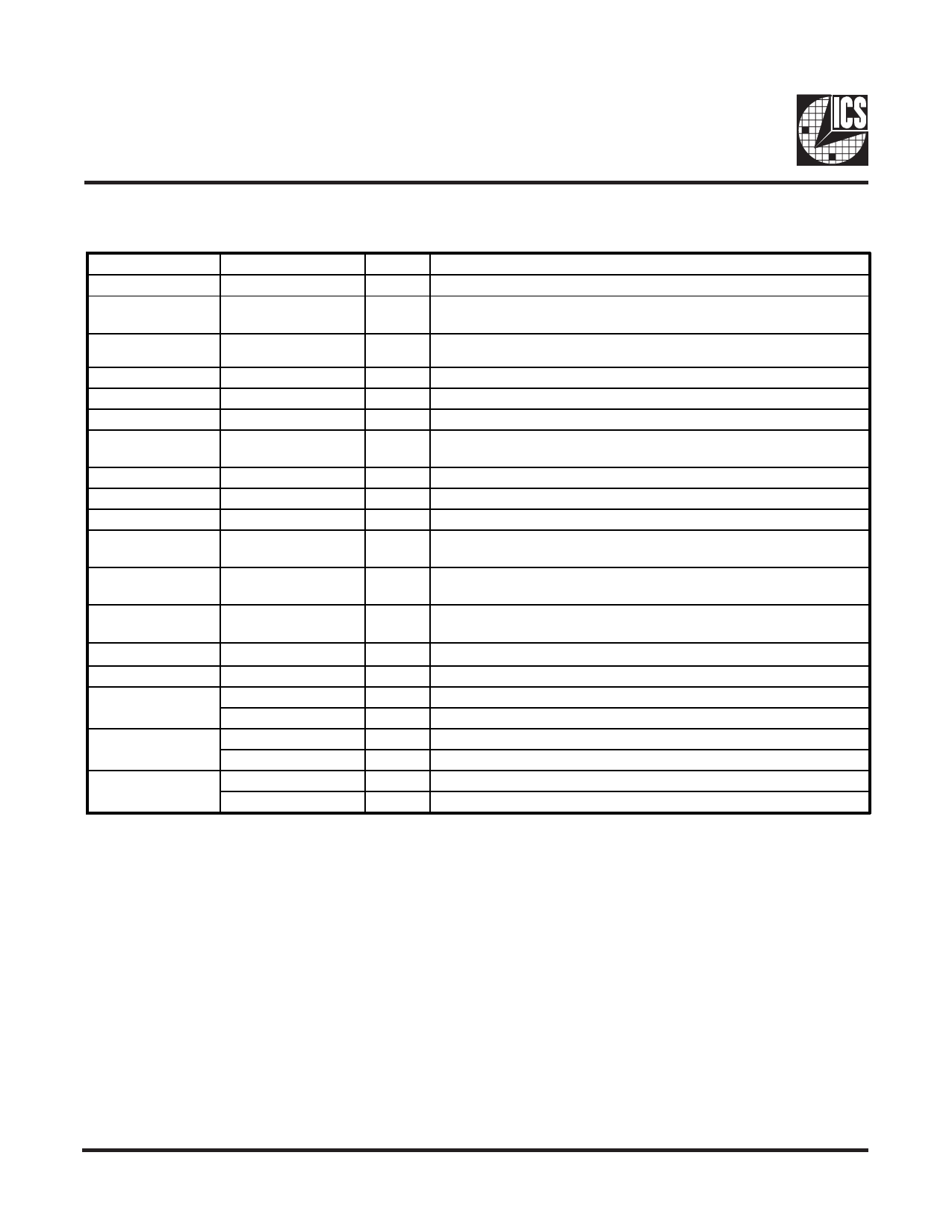

Pin Descriptions

PIN NUMBER

2

3, 9, 16, 22, 27,

33, 39, 45

PIN NAME

REF0

GND

4

X1

5

25

7

8, 10, 11, 12

13, 15

26

23

24

1, 6, 14,

19, 30, 36,

17, 18, 20, 21,

32, 34, 35, 37, 38

X2

MODE

PCLK_F

PCICLK (0:5)

OE

SDATA

SCLK

VDD1, VDD2,

VDD3

SDRAM

(0:4) (8:11)

42, 48

VDDL2, VDDL1

40, 41, 43, 44

46, 47

28

29

31

CPUCLK (0:3)

IOAPIC (0:1)

SDRAM7

PCI_STOP#

SDRAM6

CPU_STOP#

SDRAM5

PWR_DWN#

TYPE

DESCRIPTION

OUT 14.318 MHz reference clock outputs.

PWR Ground.

IN

OUT

IN

OUT

XTAL_IN 14.318MHz Crystal input, has internal 33pF load cap and feed

back resistor from X2

XTAL_OUT Crystal output, has internal load cap 33pF

Mode select pin for enabling power management features.

Free running BUS clock during PCI_STOP# = 0.

OUT BUS clock outputs.

IN Logic input for output enable, tristates all outputs when low.

IN Serial data in for serial config port.

IN Clock input for serial config port.

PWR Nominal 3.3V power supply, see power groups for function.

OUT SDRAM clocks 66.6MHz.

PWR

OUT

OUT

OUT

IN

OUT

IN

OUT

IN

CPU and IOAPIC clock power supply, either

2.5 or 3.3V nominal

CPU output clocks, powered by VDDL2 (66.6 MHz)

IOAPIC clock output, (14.318 MHz) powered by VDDL1

SDRAM clock 66.6 MHz selected

Halts PCICLK (0:5) at logic "0" level when low

SDRAM clock 66.6 MHz selected

Halts CPUCLK clocks at logic "0" level when low

SDRAM clock 66.6 MHz selected

Powers down chip, active low

Power Groups

VDD1 = REF0, X1, X2

VDD2 = PCICLK_F, PCICLK (0:5)

VDD3 = SDRAM (0:4) (8:11) SDRAM5/PWR_DWN#,

SDRAM6/CPU_STOP#, SDRAM7/PCI_STOP#, supply for PLL Core.

VDDL1 = IOAPIC (0:1)

VDDL2 = CPUCLK (0:3)

2