HFA3861A Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

Список матч

HFA3861A Datasheet PDF : 37 Pages

| |||

HFA3861A

as received from the control processor. Some dummy bits

will be appended to the end of the packet to insure an

orderly shutdown of the transmitter. This prevents

spectrum splatter. At the end of a packet, the external

controller is expected to de-assert the TX_PE line to shut

the transmitter down.

Scrambler and Data Encoder Description

The modulator has a data scrambler that implements the

scrambling algorithm specified in the IEEE 802.11 standard.

This scrambler is used for the preamble, header, and data in

all modes. The data scrambler is a self synchronizing circuit.

It consists of a 7-bit shift register with feedback from

specified taps of the register. Both transmitter and receiver

use the same scrambling algorithm. The scrambler can be

disabled by setting CR32 bit 2 to 1.

NOTE: Be advised that the IEEE 802.11 compliant scrambler in the

HFA3861A has the property that it can lock up (stop scrambling) on

random data followed by repetitive bit patterns. The probability of this

happening is 1/128. The patterns that have been identified are all

zeros, all ones, repeated 10s, repeated 1100s, and repeated

111000s. Any break in the repetitive pattern will restart the

scrambler. To insure that this does not cause any problem, the CCK

waveform uses a ping pong differential coding scheme that breaks

up repetitive 0s patterns.

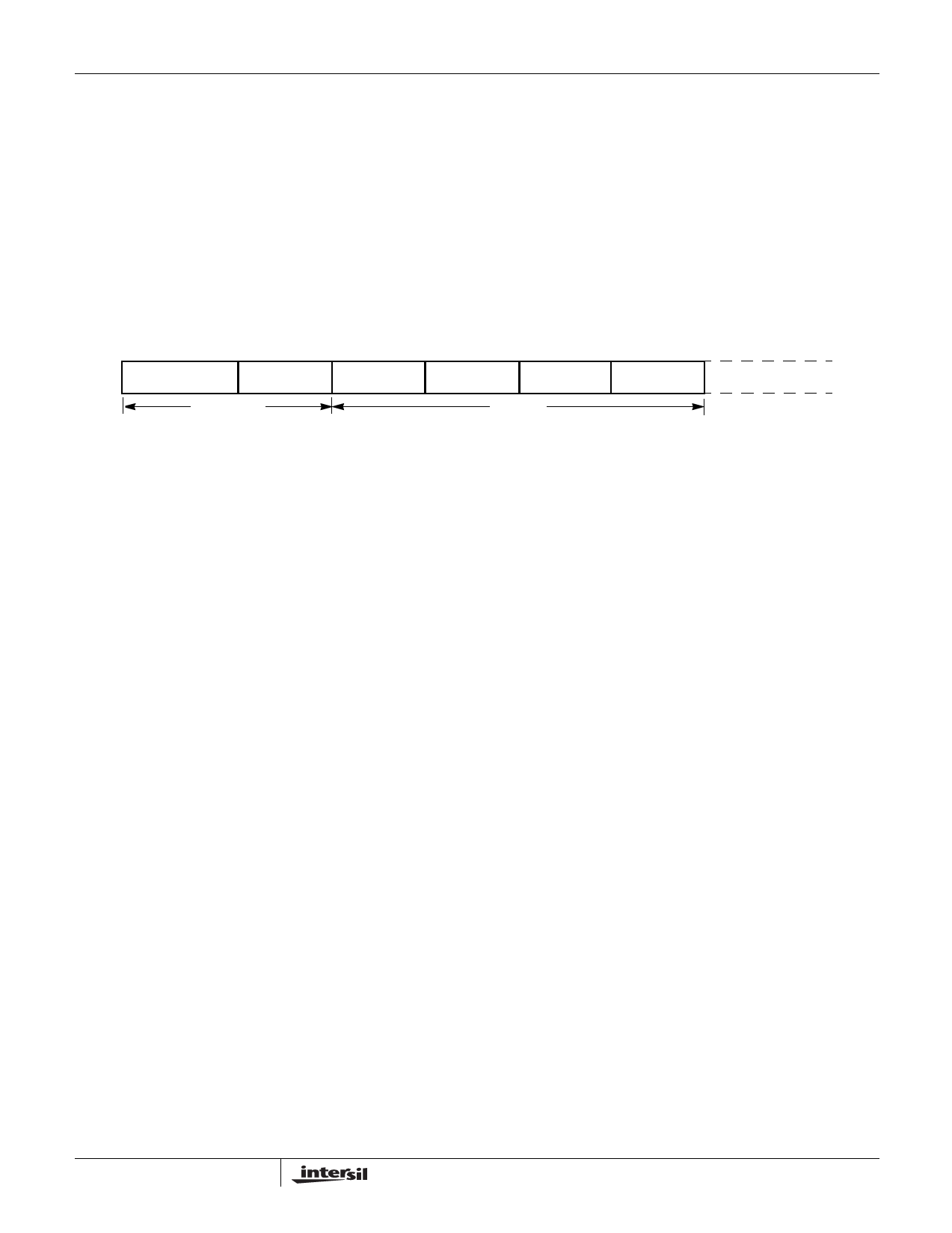

PREAMBLE (SYNC) SFD

128/56 BITS

16 BITS

PREAMBLE

SIGNAL FIELD

8 BITS

SERVICE FIELD LENGTH FIELD CRC16

8 BITS

16 BITS

16 BITS

HEADER

FIGURE 8. 802.11 PREAMBLE/HEADER

11