DS1217M Просмотр технического описания (PDF) - Dallas Semiconductor -> Maxim Integrated

Номер в каталоге

Компоненты Описание

Список матч

DS1217M Datasheet PDF : 8 Pages

| |||

DS1217M

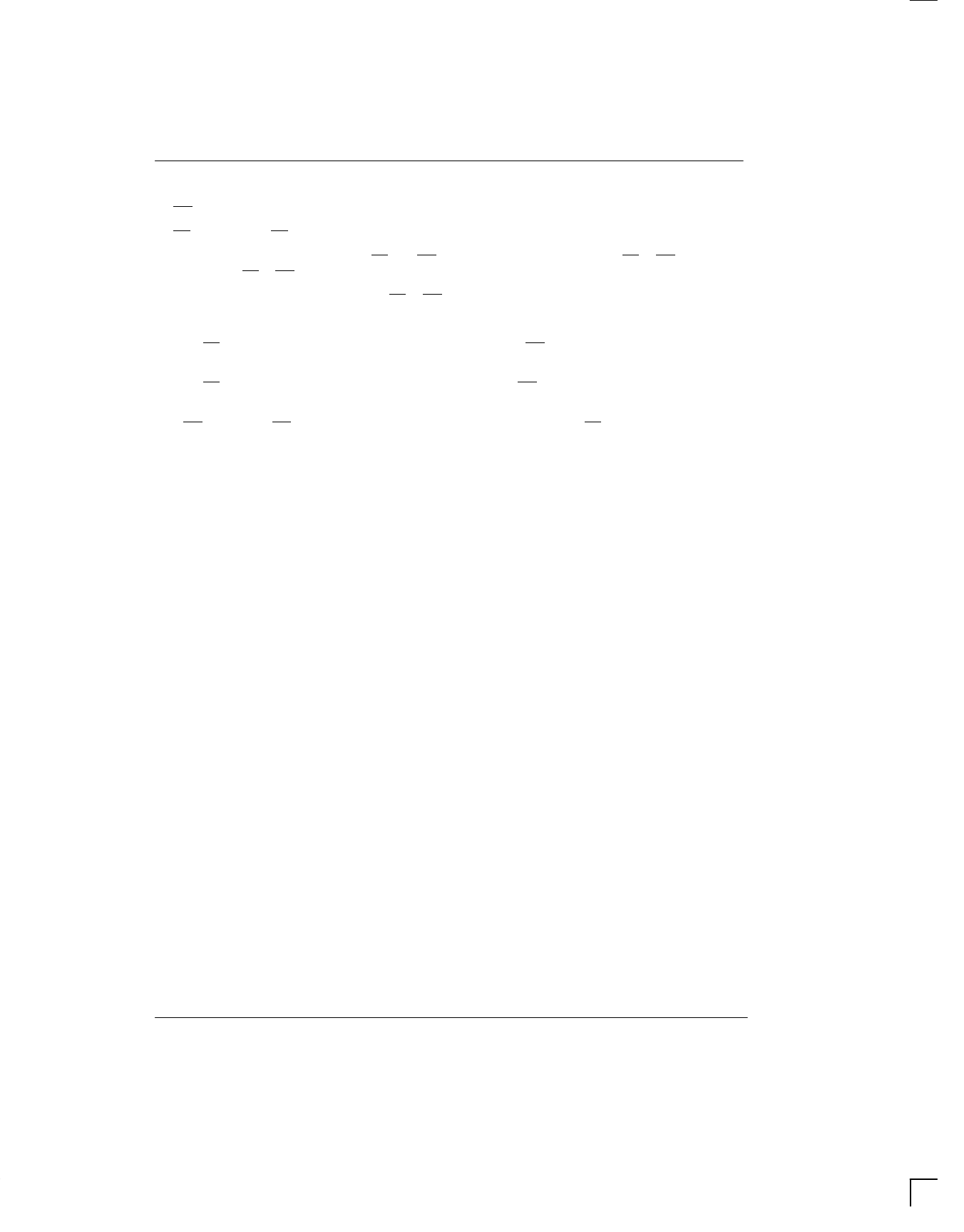

NOTES:

1. WE is high for a read cycle.

2. OE = VIH or VIL. If OE = VIH during a write cycle, the output buffers remain in a high impedance state.

3. tWP is specified as the logical AND of CE and WE. tWP is measured from the latter of CE or WE going low to

the earlier of CE of WE going high.

4. tDH, tDS are measured from the earlier of CE or WE going high.

5. These parameters are sampled with a 5 pF load and are not 100% tested.

6. If the CE low transition occurs simultaneously with or later than the WE low transition in Write Cycle 1, the

output buffers remain in a high impedance state in this period.

7. If the CE high transition occurs prior to or simultaneously with the WE high transition in Write Cycle 1, the

output buffers remain in a high impedance state in this period.

8. If WE is low or the WE low transition occurs prior to or simultaneously with the CE low transition, the output

buffers remain in a high impedance state in this period.

9. Each DS1217M is marked with a 4-digit date code AABB. AA designates the year of manufacture. BB desig-

nates the week of manufacture. The expected tDR is defined as starting at the date of manufacture.

10. Removing and installing the cartridge with power applied may disturb data.

DC TEST CONDITIONS

Outputs Open

t Cycle = 250 ns

All Voltages Are Referenced to Ground

AC TEST CONDITIONS

Output Load: 100pF + 1TTL Gate

Input Pulse Levels: 0-3.0V

Timing Measurement Reference Levels

Input: 1.5V

Output: 1.5V

Input Pulse Rise and Fall Times: 5ns

030598 8/8